本节书摘来自华章出版社《计算机组成原理》一书中的第1章,第1.6节, 作 者 Computer Organization and Architecture: Themes and Variations[英]艾伦·克莱门茨(Alan Clements) 著,沈 立 王苏峰 肖晓强 译, 更多章节内容可以访问云栖社区“华章计算机”公众号查看。

1.6 计算机系统概览

为了学习后面的章节,本节简要介绍把CPU变成计算机系统的存储系统和总线系统。计算机科学家将存储器视作一个巨大的通过地址访问的数组。例如,如果用数组M表示存储器,那么它的第i个元素可以表示为M[i]或Mi。存储器非常重要,因为它的大小(即存储容量)决定了程序能够存储的数据量,它的速度(访问时间)决定了程序的数据处理速率。在过去的50年里,程序体积不断增加,程序所使用的数据总量增加得更快。20世纪70年代的飞行模拟器就是一个很好的例子,那时它还是非常简单、仅关注基本的飞行动作(直线和水平飞行、爬升、下降和转向)。现代的飞行模拟器不仅可以完成这些基本操作,还可以生成驾驶舱和外部世界的复杂视图。而且,它还可以提供一个覆盖大部分地球表面的详细地图。这样一个程序的体积也从16KB增加到几GB。

计算机技术正在飞速进步,而存储技术从某些方面来说却严重地滞后了。例如,处理器速度的增加速率远远超过了存储器的。后面的章节将介绍如何隐藏慢速存储器带来的问题。人们提出“存储墙”一词,以说明存储性能最终会制约处理器的性能。

1.6.1 存储层次

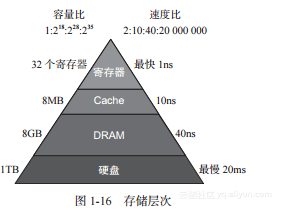

存储系统的制造技术种类繁多,在计算机中随处可见。最快的存储器能够在10-9秒内完成数据访问,最慢的则会超过100秒,性能差距为1:1011。为了便于理解,大家可以参考下面的数据:我的步行速度与导弹的速度之比约为1:104。由于CPU与存储器的性能之间的差距不断加大,设计者们试图通过在使用数据之前将它们从存储器中取出来消除相对慢速的存储器的影响,以隐藏等待时间(也叫作延迟)。图1-16给出了经典的存储层次图,展示了计算机中存储部件的类型、速度(访问时间)以及它们在PC机中的典型容量。对于每种部件,还列出了速度比和容量比。寄存器存放处理器的工作数据,Cache是缓存常用数据的快速存储器,DRAM存放工作数据块,硬盘则保存程序和数据。请注意,硬盘的容量是寄存器的4000万倍,但其速度却比寄存器慢2000万倍。在讨论存储器之前,我们会简要介绍Cache,因为它对决定计算机的性能具有非常关键的作用。

经常被用到的数据保存在Cache中,Cache的访问时间比主存短得多。Cache对计算机总体性能的影响也许与处理器体系结构的影响相同。尽管由于它的实现细节,Cache是一个非常复杂的话题,但它的基本操作却非常简单。Cache保存着主存中经常使用的数据的副本,就像笔记本和手机中保存着常用的用户名和地址一样,以便我们能方便地使用。Cache系统与计算机的地址总线和数据总线相连,监听着CPU与存储器之间的事务。

只要Cache注意到CPU发出的地址与它保存的某个数据元素的地址相同,它就会喊道:“我有这个数据!”之后把这个数据发送给CPU,并告诉存储器不要为此次访问而烦恼了。在日常生活中,如果你要给一个朋友打电话,你也会首先查看你的地址簿。如果他的名字不在地址簿中,你必须在一本更大的电话目录中查找。一旦找到了朋友的号码,你就会将它记在地址簿中,当你下次要给他打电话时就可以节约时间了。

将Cache与地址簿类比是比较准确的。地址簿非常有用,因为你经常要打电话的人数仅仅是那些有电话的人中的很小一个子集,并且你会发现你90%的电话都是打给地址簿上的人的。另一个很好的类比是当你购买了一本新的地址簿时,上面没有任何名字,当你第一次给某人打电话时,你必须把他的名字记到地址簿上。地址簿说明了Cache设计的另一个问题。假设你将所有名字以“S”开头的朋友记在“S页”上。现在,如果你碰到了某个名字也是以“S”开头的人,你就会面临一个问题。你依次查看那些以“S”开头的姓名并且说,“这家伙今年没有给我寄生日贺卡;他已经成为历史了。”按照Cache的术语,当Cache中填满数据元素时,你必须删去某个旧的数据,以便腾出空间容纳新的数据。

人类世界与Cache还有另外一种类比。你也许会随身携带一本记载了你最重要朋友的地址簿,而将另外一本放在办公桌上。当你想给某个朋友打电话时,你首先会查找你个人地址簿中的姓名。如果那里没有,你会去试着查找桌子上那本。多个地址簿类似于多级Cache。处理器会访问快速的L1(一级)Cache,它是CPU的一部分,并希望92%的信息都会在那里找到。如果数据不在L1 Cache中,则会去访问容量更大但速度更慢的L2(二级)Cache。也许在那里找到数据的概率为98%。如果这次访问也失败了,计算机也许还会去另外一个Cache中查找——三级Cache。如果那里也没有,就只能从主存中取出这个数据了。

Cache与地址簿之间也还有另外一种类比。假设某人有3个地址簿。当他结识了一位新朋友后,他会将名字写入3本地址簿中。如果这个朋友搬家了,他可能只更新了一个地址簿而忘记去更新另外两个。当他从办公室给这位朋友电话时,他可能会拨打旧的号码,因为他恰好使用了未更新的地址簿。如何保持Cache存储器和磁盘中的数据一致,是计算机设计者所关注的主要问题。

我们还会讨论存放正在执行的程序的主存。它是由一种叫作动态随机访问存储器(Dynamic Random Access Memory,DRAM)的易失性半导体存储器构成的立即存取存储器。这种存储器之所以是易失性的,是因为掉电时其中的数据都会丢失,因此不能用它长时间地保存程序。对于立即存取存储器,我们会讨论一些新兴的存储技术,特别是那种掉电了数据依然还在的非易失性存储器。这种存储器对于MP3播放器和数码相机之类的便携式应用非常重要。

1.6.2 总线

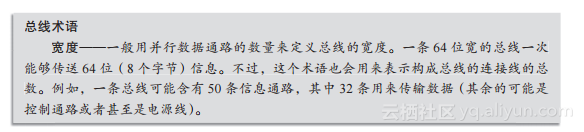

总线将计算机的两个或多个功能单元连接在一起并允许它们相互交换数据(例如CPU与显卡之间的总线)。总线还将计算机与外设连接在一起(例如将打印机接入计算机的USB总线)。总线是计算机系统非常重要的组成部分,因此《计算机存储与外设》第4章的大部分内容都用来讨论计算机总线。本节将简要介绍总线并强调若干相关概念。

图1-17描述了一个没有总线的假想系统的结构。假设其中带阴影的圆圈代表那些必须与其他单元通信的处理单元。在这个例子里,一些单元只能与另外一个单元通信,而其他单元必须与另外几个单元通信。正如读者所看到的那样,结点之间的互连复杂并且凌乱。而且,若要向该系统中增加一个新的单元,必须在这个新单元与它所连接的每一个单元之间增加一条新的连线。

图1-18展示了通过公共总线将所有单元连接在一起的好处。此时只有一条高速数据通路,每个单元通过一个接口与这条通路相连。

图1-18所示互连结构的问题在于,每次只有唯一一个设备能够与其他设备通信,因为这里只有一条信息通路。如果两个设备同时请求使用总线,它们不得不去竞争总线的控制权。我们用术语仲裁来描述这种两个或多个设备竞争同一资源(本例中是总线)的过程。一些系统使用一个名为仲裁器的专用部件来决定允许哪个设备继续工作,而其他竞争者只能等待轮到自己。

现代计算机中有多条总线,包括片内总线、功能单元间(如CPU和存储器间)的总线以及总线间的总线。

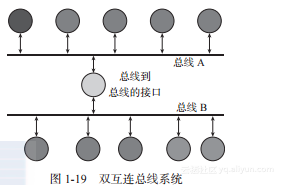

图1-19描述了一个多总线系统。处理器①通过总线A进行通信。第二条总线B,通过一个总线接口部件连接到总线A上。为什么要使用两条总线?首先,多条总线允许并发操作。例如,两个设备可以通过总线A相互通信,与此同时另一对设备可以通过总线B相互通信。一个更重要的原因在于这些总线可能具有完全不同的特点和操作速度。

一台计算机可能拥有完整的总线层次结构——每条总线都面向其预期应用进行了优化。计算机中速度最快的总线是那些与高速存储或视频设备通信的。这些总线的设计和结构必须面向速度专门优化。另一些总线则担任不同的角色(如将计算机与大量外设连在一起)。USB和FireWire总线都是非常典型的、专门为了某些功能而设计的低开销总线的实例。这些总线的通路长度比存储总线长得多。本书最后一部分将非常详细地讨论总线及其体系结构。

标准和协议是本书中两个经常讨论的主题(特别是当讨论存储接口、总线和I/O技术时)。标准是一种约定好的设计系统、定义系统或对其他任何方面进行分类的方式。标准在日常生活中非常重要。例如,为了允许人们将电子设备从一个地方移到第一个地方,电源插座和插头必须符合约定的标准。即便是我们通常不考虑的一些因素(比如机场跑道和滑行道上的灯和标记)也是标准化的,这样只要飞行员知道两个城市标记的含义完全相同,他就可以离开北京抵达波士顿。计算标准指明了插头和插座(比如USB)的物理尺寸、电压和电路表示信号,以及数据交换过程中的信号序列。

协议与标准类似,但它覆盖的范围较窄。协议决定了双方通信时各事件的发生顺序。例如,当计算机将数据发送给存储器时,写协议定义了信号序列(地址、写命令、要保存的数据)以及信号的最长和最短持续时间。

下一章将介绍数字是如何在计算机中表示的,以及适用于这些数字的操作类型。我们还会介绍基本电路元素、门和触发器,并说明如何利用它们搭建计算机的基本电路。实际上,如果将本章中对计算机的介绍与下一章中对简单电路的介绍合并在一起,读者将会了解计算机是如何工作的。尽管今天的数字计算机极其复杂,它们(原则上)仍然是非常简单的设备。其复杂性在于那些精细的细节以及试图用来加速计算机操作的手段(比如在完成测试之前对其结果进行预测)。