本节书摘来自华章出版社《深入浅出DPDK》一书中的第2章,第2.1节存储系统简介,作者朱河清,梁存铭,胡雪焜,曹水 等,更多章节内容可以访问云栖社区“华章计算机”公众号查看。

第2章 Cache和内存

2.1 存储系统简介

一般而言,存储系统不仅仅指用于存储数据的磁盘、磁带和光盘存储器等,还包括内存和CPU内部的Cache。当处理完毕之后,系统还要提供数据存储的服务。存储系统的性能和系统的处理能力息息相关,如果CPU性能很好,处理速度很快,但是配备的存储系统吞吐率不够或者性能不够好,那CPU也只能处于忙等待,从而导致处理数据的能力下降。接下来本章会讨论Cache和内存,对于磁盘和磁带等永久性存储系统,在此不作讨论。

2.1.1 系统架构的演进

在当今时代,一个处理器通常包含多个核心(Core),集成Cache子系统,内存子系统通过内部或外部总线与其通信。

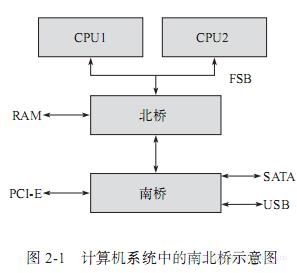

在经典计算机系统中一般都有两个标准化的部分:北桥(North Bridge)和南桥(South Bridge)。它们是处理器和内存以及其他外设沟通的渠道。处理器和内存系统通过前端总线(Front Side Bus,FSB)相连,当处理器需要读取或者写回数据时,就通过前端总线和内存控制器通信。图2-1给出了处理器、内存、南北桥以及其他总线之间的关系。

我们可以看到,该架构所有的处理器共用一条前端总线与北桥相连。北桥也称为主桥(Host Bridge),主要用来处理高速信号,通常负责与处理器的联系,并控制内存AGP、PCI数据在北桥内部传输。而北桥中往往集成了一个内存控制器(最近几年英特尔的处理器已经把内存控制器集成到了处理器内部),根据不同的内存,比如SRAM、DRAM、SDRAM,集成的内存控制器也不一样。南桥也称为IO桥(IO bridge),负责I/O总线之间的通信,比如PCI总线、SATA、USB等,可以连接光驱、硬盘、键盘灯设备交换数据。在这种系统中,所有的数据交换都需要通过北桥:

1)处理器访问内存需要通过北桥。

2)处理器访问所有的外设都需要通过北桥。

3)处理器之间的数据交换也需要通过北桥。

4)挂在南桥的所有设备访问内存也需要通过北桥。

可以看出,这种系统的瓶颈就在北桥中。当北桥出现拥塞时,所有的设备和处理器都要瘫痪。这种系统设计的另外一个瓶颈体现在对内存的访问上。不管是处理器或者显卡,还是南桥的硬盘、网卡或者光驱,都需要频繁访问内存,当这些设备都争相访问内存时,增大了对北桥带宽的竞争,而且北桥到内存之间也只有一条总线。

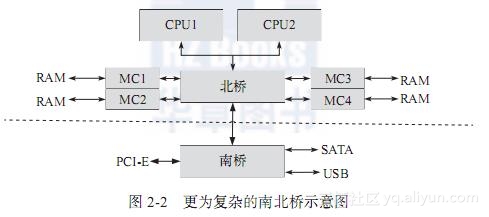

为了改善对内存的访问瓶颈,出现了另外一种系统设计,内存控制器并没有被集成在北桥中,而是被单独隔离出来以协调北桥与某个相应的内存之间的交互,如图2-2所示。这样的话,北桥可以和多个内存相连。

图2-2所示的这种架构增加了内存的访问带宽,缓解了不同设备对同一内存访问的拥塞问题,但是却没有改进单一北桥芯片的瓶颈的问题。

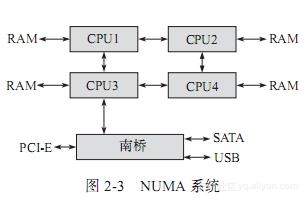

为了解决这个瓶颈,产生了如图2-3所示的NUMA(Non-Uniform Memory Architecture,非一致性内存架构)系统。

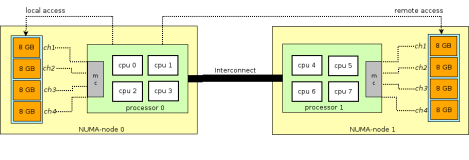

在这种架构下,在一个配有四核的机器中,不需要一个复杂的北桥就能将内存带宽增加到以前的四倍。当然,这样的架构也存在缺点。该系统中,访问内存所花的时间和处理器相关。之所以和处理器相关是因为该系统每个处理器都有本地内存(Local memory),访问本地内存的时间很短,而访问远程内存(remote memory),即其他处理器的本地内存,需要通过额外的总线!对于某个处理器来说,当其要访问其他的内存时,轻者要经过另外一个处理器,重者要经过2个处理器,才能达到访问非本地内存的目的,因此内存与处理器的“距离”不同,访问的时间也有所差异,对于NUMA,后续章节会给出更详细的介绍。

2.1.2 内存子系统

为了了解内存子系统,首先需要解释一下和内存相关的常用用语。

1)RAM(Random Access Memory):随机访问存储器

2)SRAM(Static RAM):静态随机访问存储器

3)DRAM(Dynamic RAM):动态随机访问存储器。

4)SDRAM(Synchronous DRAM):同步动态随机访问存储器。

5)DDR(Double Data Rate SDRAM):双数据速率SDRAM。

6)DDR2:第二代DDR。

7)DDR3:第三代DDR。

8)DDR4:第四代DDR。

1.SRAM

SRAM内部有一块芯片结构维持信息,通常非常快,但是成本相对DRAM很高,应用时容量不会很大,因而不能作用系统的主要内存。一般处理器内部的Cache就是采用SRAM。

2.DRAM

DRAM通常是系统的主要内存,动态表示信息是存储在集成电路的电容器内的,由于电容器会自动放电,为了避免数据丢失,需要定期充电。通常,内存控制器会负责定期充电的操作。不过随着更好技术的提出,该技术已经被淘汰。

3.SDRAM

一般DRAM都是采用异步时钟进行同步,而SDRAM则是采用同步时钟进行同步。通常,采用SDRAM结构的系统会使处理器和内存通过一个相同的时钟锁在一起,从而使处理器和内存能够共享一个时钟周期,以相同的速度同步工作。该时钟会驱动一个内部的有限状态机,能够采用流水线的方式处理多个读写请求。

SDRAM采用分布式架构,内含多个存储块(Bank),在一个时钟周期内,它能够独立地访问每个存储块,从而可以多次进行读写操作,增加了内存系统的吞吐率。

SDRAM技术广泛用在计算机行业中,随着该技术的提出,又出现了DDR(也称为DDR1),DDR2,DDR3。最新的DDR4技术标准也在2014年下半年发布。