本 节 书 摘 来 自 华 章 出 版 社 《计算机存储与外设》 一 书 中 的 第2章,第2.2节, 作 者 Computer Organization and Architecture: Themes and Variations[英]艾伦·克莱门茨(Alan Clements) 著, 沈 立 肖晓强 王苏峰 译, 更 多 章 节 内 容 可 以 访 问 云 栖 社 区 “华 章 计 算 机” 公 众 号 查 看。

2.2 主存储器

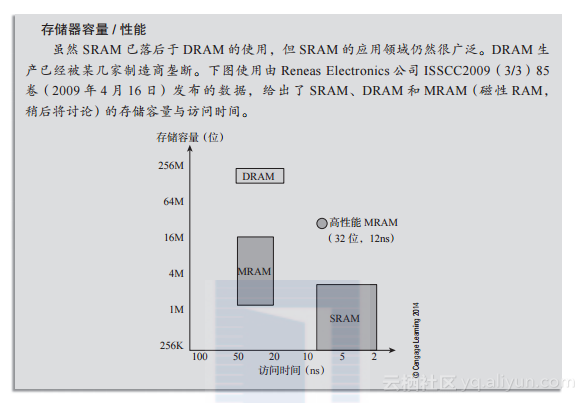

这一节将介绍直接访问存储器(immediate access store)或者主存储器(primary memory)。没有低成本、高速的存储器,实现复杂的操作系统和应用(例如Photoshop)是十分困难的。本节首先介绍静态存储器(SRAM),因为它在动态存储器(DRAM)之前出现且比DRAM更容易理解。实际上,Cache存储器通常由SRAM实现。

2.2.1 SRAM

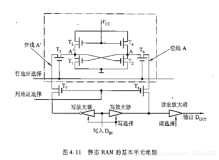

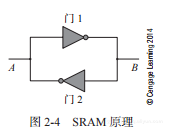

图2-4说明了SRAM概念上是如何工作的。两个反向器端端相联构成一个环。门1的输入是A,其输出B=,这又是门2的输入。门2的输出是A,其中A===A,这也是门1的输入。门1的输入是由门1的输入经过反馈产生的。这是一个自主维持存储器(self-sustaining memory)。无论初始给门1何种输入,其反馈都会使这种状态得到维持。

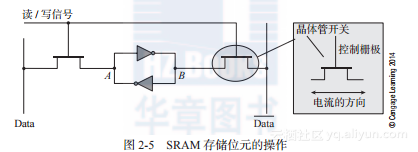

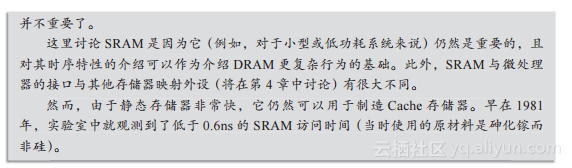

图2-5显示了如何将图2-4中的两个交叉耦合的反向器变成实际的静态存储位元。作为开关的两个晶体管连接到反向器电路的左边和右边,用于访问存储单元(右边的阴影插图显示了晶体管有3个端子;在控制栅极的信号电平决定了另外两极之间的路径是打开还是关闭)。当读/写信号线是低电平,这两个晶体管都处于打开状态,数据信号线Data和都没有被反向器驱动(即被控制)。

数据写入位元时,将要写的一位数据及其取反值分别放在Data和信号线上,然后发出读/写信号。反向器节点A和B被修改为所期望的值,当读/写信号为低电平时保持写入的数据。当进行读操作时,首先发出读/写信号,使反向器的输出与数据信号线连接,然后读取A节点的电平信号即可。

因为一个反向器需要由两个串联的晶体管来实现,所以每个静态位元需要6个晶体管存储一位数据。实际的静态存储器为m×n的位元阵列。访问位元时需要指定其行和列地址。因此,一个n位的静态存储单元需要6n个晶体管加上用于行列地址解码以及执行各种信号控制与保持操作所需的晶体管。

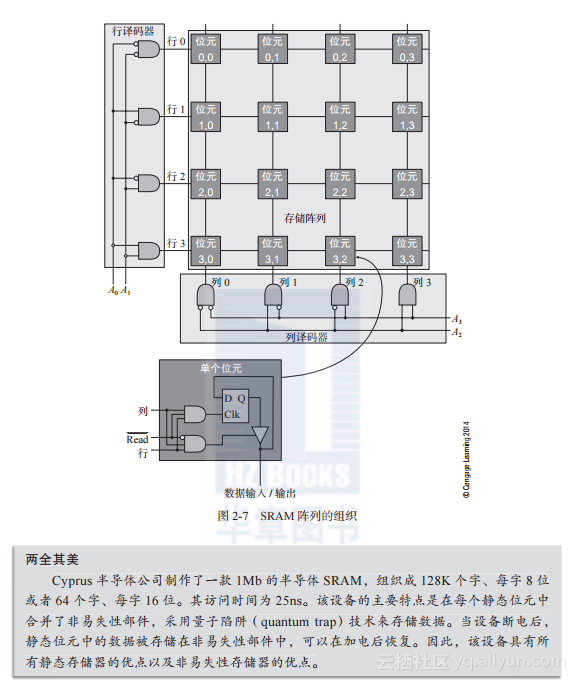

有些静态存储器每个位元只需使用4个晶体管。无论怎样,n位静态存储器位元需要4n或6n个晶体管。而动态存储位元只需要一个晶体管,这意味着动态存储器的密度至少可以达到静态存储器的4倍。图2-6给出了由6个晶体管构成的静态存储位元的电路图。图中用插图的形式将DRAM位元与其进行对比。静态存储器的速度比动态存储器的速度要快。

半导体技术的进步总是在继续。2001年,日本富士通实验室的研究人员公布了一款由铟镓砷化物(与常见的半导体材料硅对比是一种很专业的物质)构成的单晶体管静态存储位元的设计,可以工作在77K(-196℃)。这样的温度对当前的实际应用来说都太低。它可以通过量子隧道(quantum tunneling)效应来存储数据。一些其他技术,如纳米管,可能是未来高密度、低功耗存储器的可能竞争者。

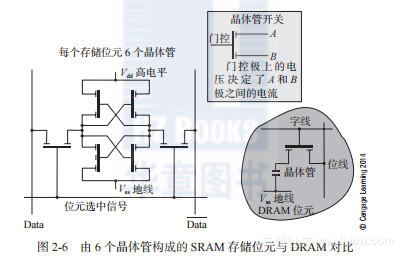

一种实用的半导体SRAM芯片由独立的存储位元阵列构成。图2-7给出了一个16位的存储阵列(真正的静态存储阵列可能包含224个位元)。4位存储器地址A0~A3被分为行、列地址。二–四译码器对两位行地址进行译码后选中一行。

同时,列译码器选中4列之一。每行和每列的交叉处是存储位元,根据信号的状态进入读或写周期。这个阵列说明存储器操作是以前面介绍的逻辑部件的形式进行的。存储阵列的实际实现将使用图2-6中所示的存储位元。

1. SRAM存储系统

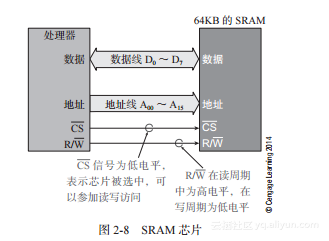

下面来看看如何使用静态存储器。RAM芯片被组织成一位宽、半字节宽(4位)、字节宽(8位)或16位宽的设备。图2-8给出了一个容量为512Kb的SRAM,它有64K字,每个字8位。它有16条地址线A0~A15,可以选择216=64K个位置,它还有8条数据线D0~D7可以在一个读周期内将8位数据交给处理器,也可以在一个写周期内从处理器接收8位数据。

访问SRAM之前需要在地址总线上给出一个地址,由一系列0和1的组合定义访问位置,然后要么在读周期中将数据交给数据总线,要么在写周期中从数据总线读取数据。

SRAM的操作通过两个信号和控制。决定了芯片是参加读周期(=1)还是写周期(=0)的操作。低电平有效的片选信号确定该芯片是参加读或写访问,还是保持空闲状态。一般情况下,为高电平,此时信号被忽略。当为低电平时,芯片参与读还是写操作取决于信号。在读周期中,可以控制存储器三态缓冲器的输出(参见《计算机组成原理》第2章)。

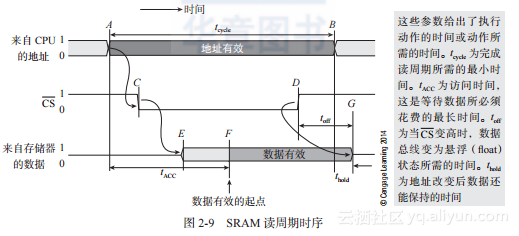

图2-9给出了SRAM的时序图(timing diagram),说明在读操作期间事件发生的顺序。时序图表明,为保证正确的存储器操作,信号必须保持的最小时间,并指出活动从开始到结束之间可能的最大持续时间。图中带箭头的线表示因果系;例如,当在C点变低(原因)使数据总线驱动器在E点被打开(结果)。

假设最初(图的左边)为高,在整个操作期间保持1状态。在图2-9中没有表示出来。

在图2-9中的A点,地址总线通过改变状态为当前读操作提供一个有效地址。这种状态的变化由地址线的交叉部分表示。一旦地址信号稳定下来,片选信号在C点指出开始进行存储器访问。由于为高电平,故为读操作周期。

为高与为低的效果导致存储器把数据放到存储器的数据总线上。数据总线结束悬浮状态,数据在E点开始出现在总线上。然而此时数据仍然是无效的,因为数据的访问时间尚未开始。

在F点,地址信号变为有效后,经过tACC秒,数据可以被处理器读取。在D点,处理器将变成高电平以完成读周期,在点G数据总线再次变成高阻的悬浮状态。从B点改变地址到数据在G点发生变化的时间称为数据保持时间(data hold time)。数据保持时间定义为地址和(或)控制信号发生改变后,数据总线上数据的保持时间。某些系统需要正的(非零)数据保持时间以保证数据可以被可靠地获取。

2.写周期

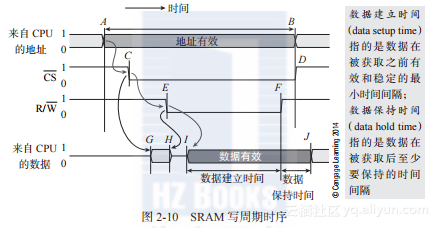

图2-10给出了一般的SRAM写周期的时序图,它比相应的读周期更复杂(这情况对所有的存储设备来说都存在)。每个芯片的具体实现不同,但基本原理是相同的。要存储的数据先放到数据总线上,然后和变为低电平以启动写周期。

图2-10中,地址总线在A点开始有效直到写周期在B点结束。假定在C点变为低电平。此时,仍然为高电平,数据总线处于悬浮状态。

访问在C点开始,但对RAM而言,只要为高电平就表示是读周期。因此,在点G,RAM开始用读出的数据驱动数据总线。当然,此时的数据是无效的,因为数据的访问时间尚未开始。

在E点,处理器使变为低电平表明当前周期是写周期。存储器终止已经开始启动的读周期,并在点H停止用读出的数据驱动数据总线。可见,存储器在点G和H之间给出了假的数据。系统设计师必须保证,此时没有其他设备使用总线。

在点I,处理器将要保存的数据放到数据总线上。写周期的关键点为F点,此时信号的上升沿表示开始捕获数据。数据必须在的上升沿之前有效,并保持到低电平变为高电平之后,此段时间为数据保持时间(data hold time)。真正SRAM的设计以或中的任何一个变为高电平来终止写周期。

介绍完了SRAM,自然就应该介绍DRAM。但是在这之前,还应该顺便介绍影响所有存储器系统设计的两个问题,无论是静态/动态、读写/只读存储器。这两个问题就是字节/字控制以及地址译码的使用。

3.字节/字控制

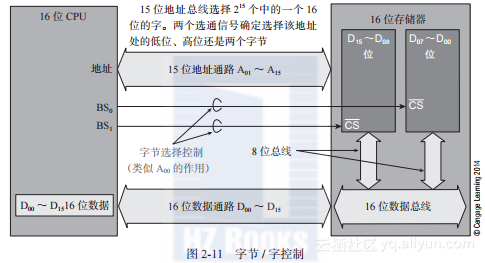

20世纪70年代,微处理器都是按字节宽度设计的,数据总线为8位宽。地址总线为16位,使用A15~A00这些地址线可以选定216=64K个字节。当出现了16位处理器后,情况变得更复杂,此时需要访问字节和16位的字(记住,存储器是以字节编址的,无论字长是1个、2个、4个还是多个字节,都可以访问存储器中的一个字节)。

由于微处理器设计者既希望访问单个字节又希望具有访问16位的能力,故他们实现了字节控制机制允许访问单个字节或者选中的字。一种典型的机制是使用地址总线选中一个16位的字(或32位或64位),然后使用字节控制线(byte control line)选中该地址处的一个或多个字节。图2-11给出了一种可能的实现,通过地址线A15~A01来选中215个16位的字。

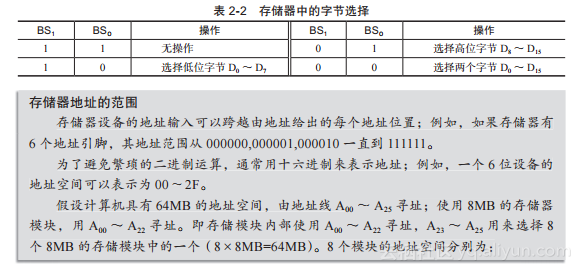

地址线A00没有使用,因为每个地址总是选中两个字节;即地址为0,2,4,6,8,…,215。两个字节选通信号BS0和BS1控制选中字的奇数字节还是偶数字节,或者同时选中两个字节(参见表2-2)。

4.地址译码

本节将简介地址译码技术,它是将地址映射到处理器物理地址空间中的方式。这里使用《计算机组成原理》第2章中的概念(二进制、十六进制以及简单的逻辑)。因为地址译码多是嵌入式系统设计师而不是计算机设计师要考虑的事情,有些读者可能希望忽略这部分内容。

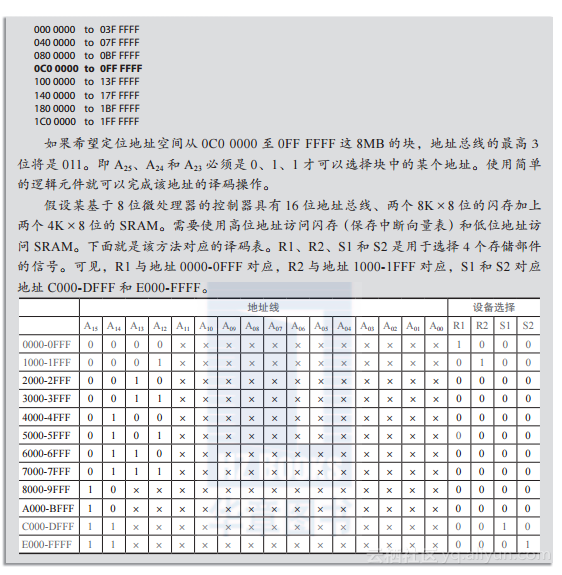

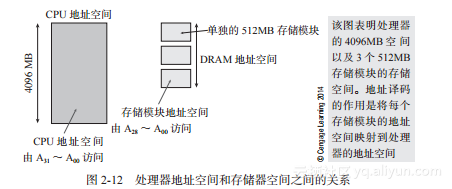

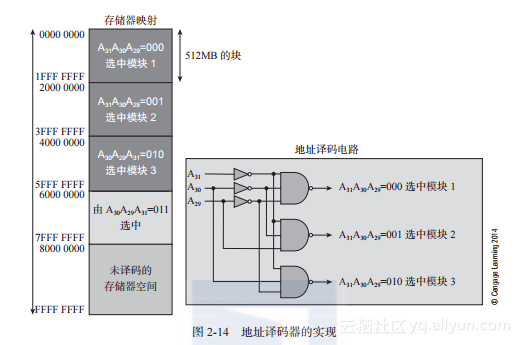

在所有可能中最好的情况是,计算机具有n位地址总线可以访问2n个字,同时存储部件有n位地址输入和2n个存储器位置。实践中,实际系统可能有几种不同的存储设备连接到处理器的总线。如果计算机处理器有32位地址总线,可访问232个字节,其存储模块(存储器的基本元件为一个芯片,而存储模块是一个包含多个存储芯片的电路板)提供229个字节(512MB)的存储;即需要232/229=23=8个模块来满足处理器的空间需求。此时需要一种将存储模块的地址空间映射到处理器地址空间的方法。称为地址译码器的电路用来检测对特定存储模块的访问,一旦CPU产生的地址落在某存储模块的地址空间中,则将该模块对应的信号变为有效。

图2-12说明了为什么需要地址译码。假设处理器使用地址线A00~A31访问4096MB的地址空间;即232=4096MB。该系统采用3个512MB的存储模块,每个模块由地址线A00~A28访问。

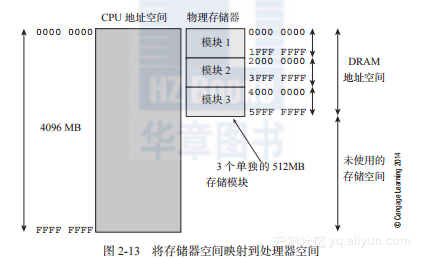

图2-13显示了这3个512MB的模块是如何映射到处理器的存储空间中的。虽然已将模块映射到存储空间相邻的区域,但没有规定物理存储器必须被映射到相邻的块。当然,如果存储区域不连续,程序员或操作系统在加载程序和数据时就需要特别小心。模块1分配的地址空间为0000 0000到1FFF FFFF,模块2的为2000 0000到3FFF FFFF,模块3的为4000 0000到5FFF FFFF。当然,每个512MB的块都是由A00~A28访问。

图2-14显示了如何设计执行存储模块映射到处理器地址空间的逻辑。3个模块中的每个模块的29个地址线都与处理器A00~A28连接在一起。用从处理器那里剩下的3根地址线A29~A31选择某存储模块,即这些地址线产生的信号可以选中对应的存储模块。

第一块存储器512MB空间的地址为0000 000016至1FFF FFFF16。该模块在A31A30A29=000时被选中。同样,第二块存储器空间的地址为2000 000016至3FFF FFFF16,该模块在A31A30A29=001时被选中。

这里不再进一步探讨地址译码,因为这是系统设计者和电子工程师要考虑的问题。地址译码可以用来匹配存储部件和CPU的地址空间,它还可以做得更多。例如,可以在多个存储器模块之间实现切换来保证任务在物理上是彼此分离的(一种内存管理的形式)。

2.2.2 交叉存储器

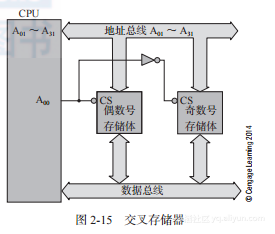

如果存储器的访问时间为tacc,则不能减少其访问时间。但是可以通过交叉(interleaving)来减少有效存取时间(effective access time)。若某存储位置在T0时刻开始访问,则数据在tacc时间后变为有效。在同一存储模块内另一个位置处的数据至少要再等tacc时间后才能获取。但是,可以同时访问其他的存储模块;即并行访问多个存储器模块。

图2-15说明了这种交叉的效果,图中两个存储体并行排列。如果在T0时刻访问第一个存储体,数据在tacc时间后变为有效。如果在T0+tcyc(其中tcyc为时钟周期时间)时刻访问第二个存储体,则第二个数据元素在T0+tcyc+tacc时间后有效。如果tcyc<tacc,则可以比在没有交叉时更早地完成第二次访存任务。只有在一个存储体访问数据时能够产生另一个存储体中操作数的地址时,有效的交叉才能实现。

存储交叉技术被称为低位交叉,其中存储地址的低位用来选择存储体。假设处理器有32位地址总线和64位数据总线。地址位A03~A31用来选择存储器中的一个字,地址位A00~A02(通过字节选通信号)用来选中当前字中的一个或多个字节。使用地址位A04执行存储体选择,所有奇数号地址的数据字从一个存储体中取出,而所有偶数号地址的数据字从另一个存储体中取出。如果使用两个地址位来实现交叉,则可以实现4个存储体并行访问。在现代微机中,双通道或三通道内存的原理同交叉的原理相同,允许同时访问2~3个DRAM存储模块。

下面将介绍DRAM的工作原理。通过几代DRAM设备的不断发展,它们基于相同的基本工作原理,但使用不同的技术来降低平均访问时间。下面将介绍基本的DRAM,讨论其不同的变种,如页模式DRAM、半字节模式DRAM、EDO存储器、SDRAM和DDR DRAM。