数字电路逻辑设计摘要

简介:

数字电路逻辑设计摘要BCD码Binary Coded Decimal, 使用二进制码(4位)的形式来表示(一位)十进制有权BCD码: 8421, 2421等无权BCD码: 余3码等一个逻辑表达式的功能表达方式通过真值表显示通过真值表我们已经知道了该表达式的逻辑功能, 现在我们根...

数字电路逻辑设计摘要

BCD码

- Binary Coded Decimal, 使用二进制码(4位)的形式来表示(一位)十进制

- 有权BCD码: 8421, 2421等

- 无权BCD码: 余3码等

一个逻辑表达式的功能表达方式

- 通过真值表显示

- 通过真值表我们已经知道了该表达式的逻辑功能, 现在我们根据真值表画出卡诺图得出最小项 \(\to\) 我们的表达式

最小项的重要性

- 现在给出一个逻辑表达式式: AB + BC, 现在要我们通过设计一个电路实现这个表达式

- 该表达式中有ABC三个变量, 我们需要有三个输入, 在观察AB发现, 这个使用C的值我们似乎(其实是可以确定的)无法确定, 现在就是最小项发挥作用的时候了, 通过将原来的表达式转换为一个最小项表达式, 式子中所有的单元都是有这3个变量组成的而没有缺省项, 这样我们在设计电路的时候就会清楚很多

- 最小项表达式是画出卡诺图的前提, 而我们画出卡诺图的目的就是为了化简, 因此可以说最小项表达式可以方便我们化简电路

求解一个函数(F)的最小项表达式

- 下面的几个的前提都是先求出F的最小项表达式

- 求解F非的最小项表达式:

- 求解F*的最小项表达式:

- F的最小项表达式中的每一个项与F*的最小项表达式中的每一个项的和为\(2^n - 1\)

实际电路设计中

译码器

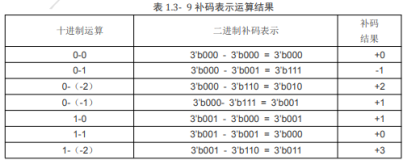

全加器与半加器

- 区别: 全加器考虑到了进位, 而半加器不考虑进位

- 对于1位(几位指的有几个信号组成的)的全加器画出真值表, 对于多为的全加器好像不好画(那就不画了)