FPGA设计中遇到的奇葩问题之“芯片也要看出身”(三)

众里寻他千百度,蓦然回首,那人却在,灯火阑珊处

工程师都知道,寻找好板和坏板之间的“差异”是定位问题的利器之一啊。因此当时虽然没有欣喜若狂,但是也隐隐看到了一丝曙光。

我冲出实验室,一溜小跑去了焊板实验室。找到了焊板的同事,让他现场给我焊两块单板,一块必须用产自大马的FPGA,一块必须用产自台湾的FPGA。那个老兄很奇怪的看了我一眼,然后又一眼。后来我才想明白估计我是第一个在乎芯片产地的怪咖。

我就站在他旁边,看着他工作,觉得时间过得奇慢无比。拿到了焊好的两块板子,又以百米冲刺的速度杀回实验室,隐隐约约听到有同事在抱怨:发哪门子神经,刮这么大的风。我以迅雷不及掩耳盗铃之势,先把台湾板子安装好,上电启动、加载、运行,果然是好的;拆掉台湾,换上大马板子,上电启动、加载、运行,果然出误码了。问题确诊了!为了保险起见,我从坏板和好板堆里各取了两块单板进行了验证,现象是一致的。

此时距离下班也就十几分钟了,我赶紧去了老大的工位,强压着鸡冻滴小心情,向老大汇报:“老大,告诉生产那边,发货只能用产自台湾的芯片,马来西亚的坚决不能用。我怀疑产自马来西亚的芯片的容差小,产自台湾的芯片的容差比较大。而设计本身肯定存在时序打擦边球的情况,导致使用产自马来西亚芯片的单板会出误码,而使用产自台湾的芯片则没有问题。到底是哪里的时序存在擦边球的隐患,我还需要进一步熟悉代码,寻找之而修改之而长治久安也”。老大难得的露出了笑容:“嗯,不错不错!这两周辛苦了,回去好好休息,下周全力解决问题。啊,对了,你该刮胡子了。”

周末跟老婆(那时候还是女朋友)去搓了一顿大餐,逛街,看电影,累得半死,但是心情那是相当的愉快。

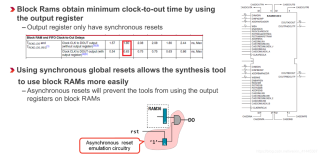

我从实验室回到了工位,在感受人间烟火气的同时,全力看代码。认真的看了一整天之后,我发现前同事对于“同步”、“组合逻辑嵌套层次不能过多”等设计原则完全不care,隐患到处都是,要想彻底的解决这些隐患,只有一个办法:推倒重来。我去找老大说明了想法,老大说:“要不要这么夸张?劳资派你去解决问题,你解决问题就是了,搞这么大工程出来,有必要么?”我说:“老大,我以一个工程师滴半生清誉担保:如果不推倒重来,问题根本不能彻底解决。”老大无奈的挥了挥手,说话的同时目露凶光兼咬牙切齿:“是否推倒你来定。但素,市场那边给出的预测是最多三个月内,这块单板就会迎来发货高峰,到那时无论如何也要保证FPGA不出任何问题。你有信心滴干活?”“饿夫考斯啊老大,没有金刚钻,不揽瓷器活啊”,我心说:“你要是答应给我加五百块工资,没准儿我敢承诺一半的时间就给你搞出来”。

结果不到三个月,我的全套重写的代码就完成了,编译、加载、测试:不论是产自台湾的芯片还是马来西亚的芯片,完全没问题。老大不放心,特地多找了几块焊着马来西亚芯片的板子一遍又一遍的测试,结果仍然是no problem at all。

老大笑靥如花(港版那个),眼睛眯成了一条缝儿:“小样儿,行啊!”我只顾嘿嘿傻笑,结果忘了趁热打铁跟老大提加薪。曾经有一个机会摆在我面前,我没有珍惜。如果有重来一次的机会,我特么会加一个十万光年的期限。

过了没多久,Xilinx公司也发来了报告:由于马来工厂的某个车间顶部一个窗户没关严,导致车间纯净度不够,所以那段时间生产的芯片尽管各项指标都在合格范围内,但是都在边缘,从而容差能力都比较低。公司已经发现并做了相应处理,之后生产的芯片从一致性方面跟台湾产的芯片没有区别了。

Well,这就是我从业生涯中碰到的“芯片也要看出身”的“灵异”事件。给我的印象是如此之深,18年后我仍然记得清清楚楚。问题解决是在2000年的9月份,第二年,我惨遭表扬,获得了某公司的最高荣誉:XXXX奖。

后记:

1、 真实问题定位的过程很痛苦,也比文中描述的要复杂,因为那批单板使用的FPGA芯片还有另外一个产地:韩国。在定位问题的过程中,台湾和韩国的芯片加载原同事的设计都没有问题,马来产的就不行。于是比对、比对、再比对,最终确定了问题出在马来产的芯片上。

2、 我重写后的设计完全不区分芯片的产地。采用原同事设计、已经发货的那批单板,使用产自台湾、韩国的芯片而暂时没出问题的,总量大概几千块吧,这些单板在条件发生变化时(比如温度变化、电压变化),出误码是必然的。好在那时候运营商对国产厂家都比较宽容,用服的同事找了各种机会,神不知鬼不觉的对这些单板上的FPGA重新加载了新版本,彻底消除了隐患。

3、 9000多行代码,我用了大概70个工作日进行了重写,计算开发效率,大约是130行/人天。实际上,我做过个人职业生涯的不完全统计:使用HDL开发FPGA,从全流程的角度来计算(从需求分析到最终发布),效率不会超过20行/人天,跟软件开发效率大致类似。当然,随着新的设计语言以及工具等方面的进步,开发效率会逐步提升是毫无疑问的。

4、 文档真的很重要、很重要、很重要。很多人会说:整个设计(模块)我闭着眼睛都能知道哪行代码是干嘛的,文档意义不大。但素,人的记忆是会衰退的。如果设计天衣无缝、没有任何问题,在整个生命周期里没有任何升级或者功能变动,那么文档也许没那么重要。但素,大家想一想,对于FPGA来说,上述条件全部满足的概率是不是和行星撞地球差不多?我几乎重写了整个设计文档,基本能保证文档描述的是西施,而设计至少是凤姐。