计算能力:

计算设备的一般规格和功能取决于其计算能力(请参阅计算能力)。

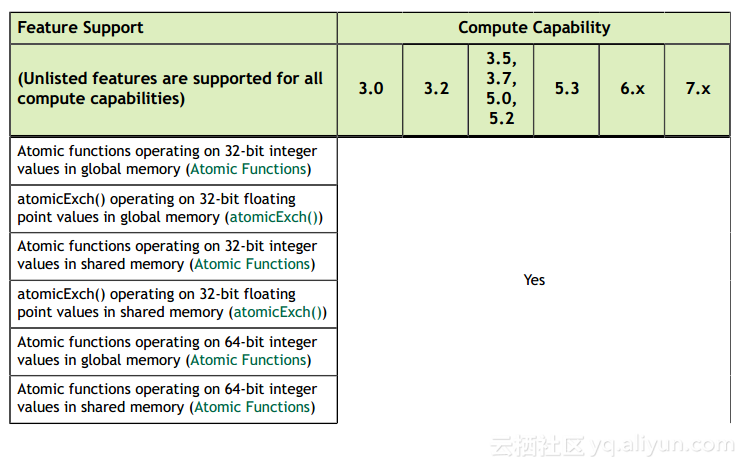

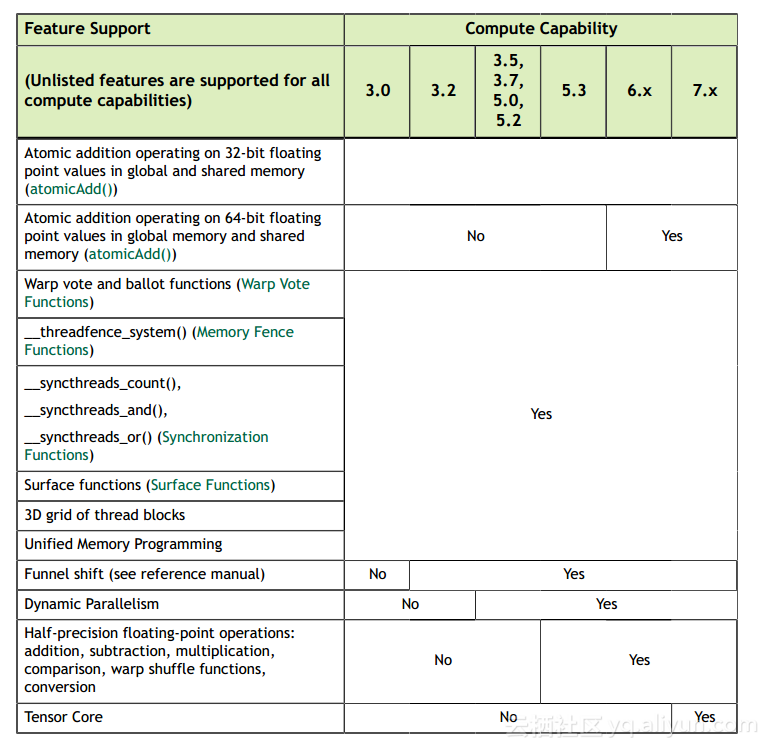

表13给出了与每个计算能力相关的功能和技术规格:

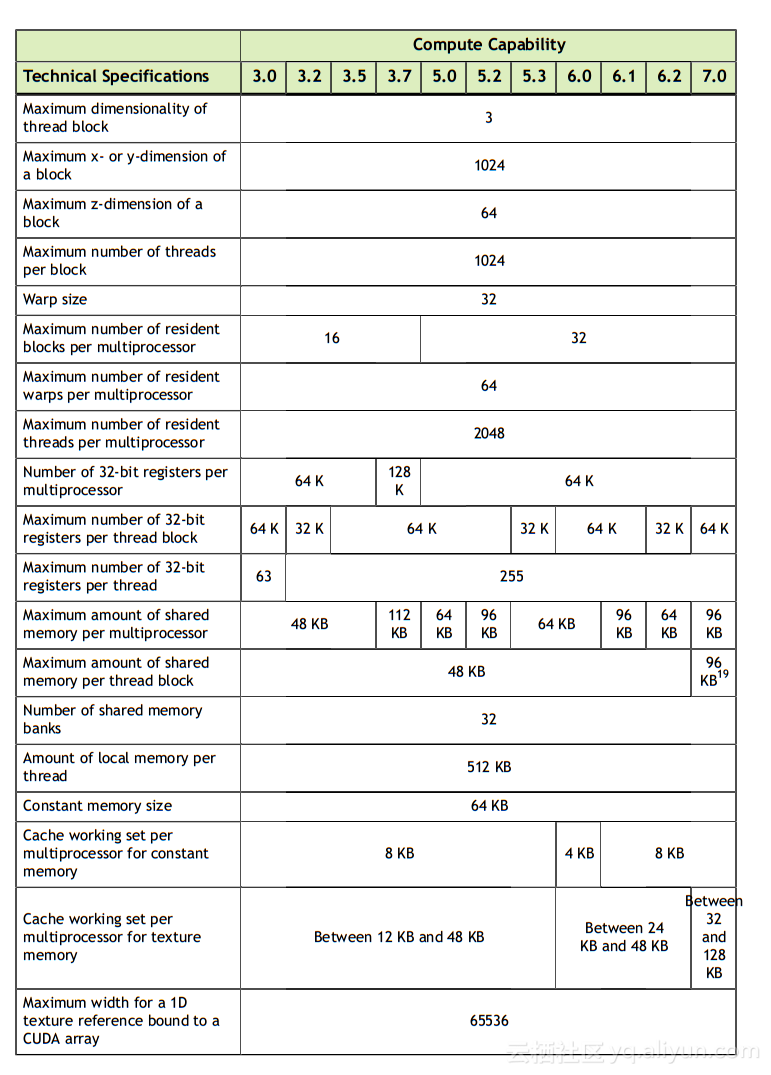

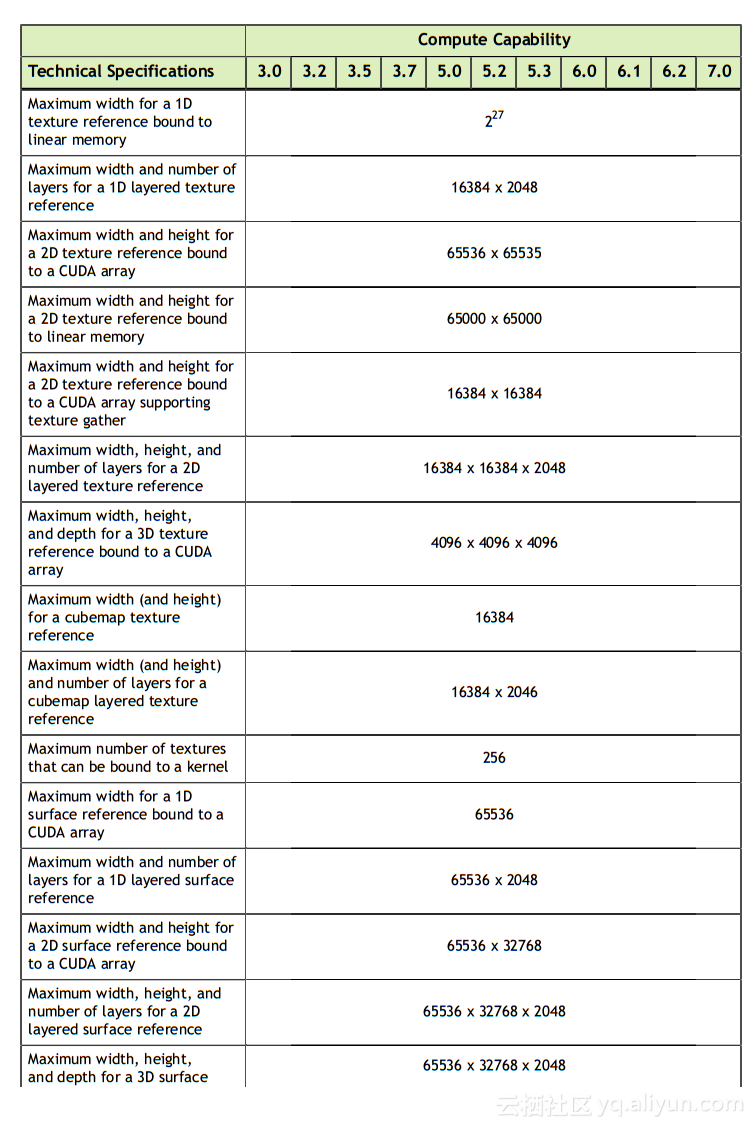

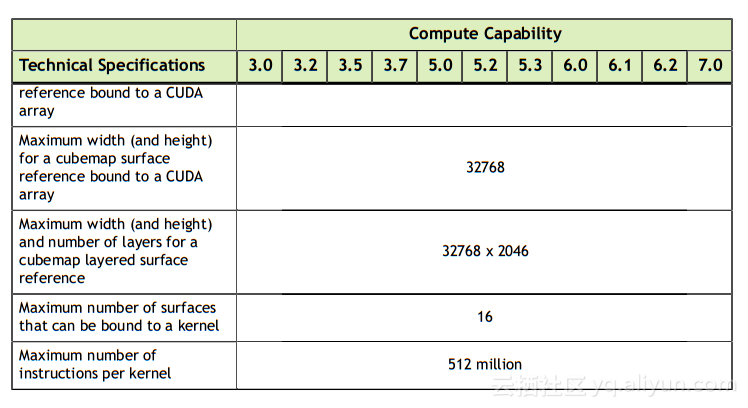

表14每个计算能力的技术规格:

浮点标准:

所有计算设备均遵循IEEE 754-2008二进制浮点运算标准,并具有以下偏差:

- 没有动态可配置的舍入模式; 然而,大多数操作支持多种IEEE舍入模式,通过设备内在函数暴露出来;

- 没有检测到发生浮点异常的机制,并且所有操作的行为就像IEEE-754异常总是被屏蔽一样,并且如果存在异常事件则传递IEEE-754定义的屏蔽响应; 出于同样的原因,虽然SNaN编码得到支持,但它们不是信号传输,并且处理得很安静;

- 涉及一个或多个输入NaN的单精度浮点运算的结果是位模式为0x7fffffff的安静NaN;

- 对于NaN,双精度浮点绝对值和负值不符合IEEE-754; 这些通过不变;

必须使用-ftz = false,-prec-div = true和-prec-sqrt = true编译代码以确保符合IEEE标准(这是默认设置;有关这些编译标志的说明,请参阅nvcc用户手册)。

无论编译器标志-ftz的设置如何:

- 全局存储器上的原子单精度浮点加法总是以清零模式运行,即,其行为等同于FADD.F32.FTZ.RN,

- 共享内存上的原子单精度浮点加法总是以非规范支持操作,即,表现等同于FADD.F32.RN.

根据IEEE-754R标准,如果fminf(),fmin(),fmaxf()或fmax()的输入参数之一是NaN,但不是另一个,则结果是非NaN参数。

在浮点值超出整数格式范围的情况下,将浮点值转换为整数值由IEEE-754决定。 对于计算设备,其行为是限制到支持的范围的末尾。 这与x86架构行为不同。

IEEE-754未定义整数除零和整数溢出行为。 对于计算设备而言,没有机制来检测是否发生了这种整数运算异常。 整数除以零产生未指定的机器特定值。