3.8 实数算术

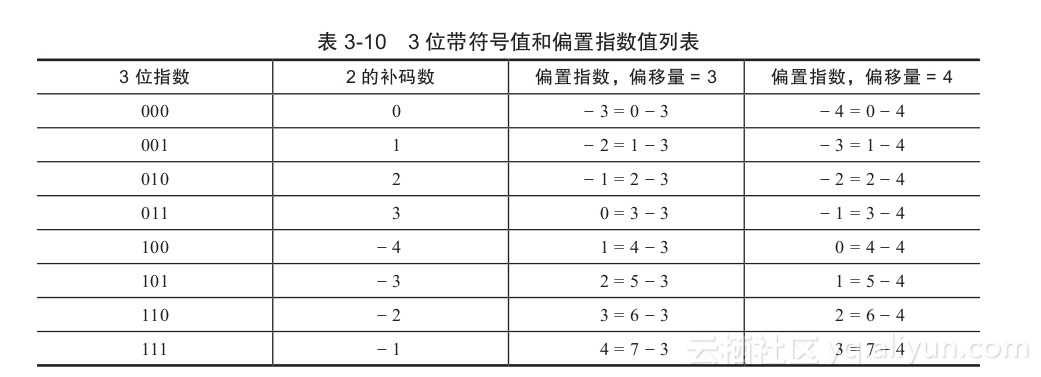

在第1章中已经简要地讨论过实数,例如,浮点数的表示方法。表3-10作为一个例子展示了3位指数值的3种不同表示方法,分别为2的补码有符号数、偏移量为3的偏置数和偏移量为4的偏置数。这三种指数表示法的指数范围分别为- 4~ + 3、偏移量为3时的

- 3~ + 4和偏移量为4时的- 4~ + 3。

通常情况下,使用偏置指数能让设计者有更多的自由来决定计算机系统中实数的集合。在这个例子中,当偏移量为3时,最大正指数为4,而当偏移量为4时,最大正指数为3。类似地,当偏移量为3时,最小负指数为- 3,当偏移量为4时,最小负指数为- 4。这表明了当偏移量为3时,将有更多可以表示为浮点数的实数> |1|(绝对值),但当偏移量为4时,将有更多可以表示为浮点数的实数< |1|(绝对值)。

3.8.1 浮点数标准

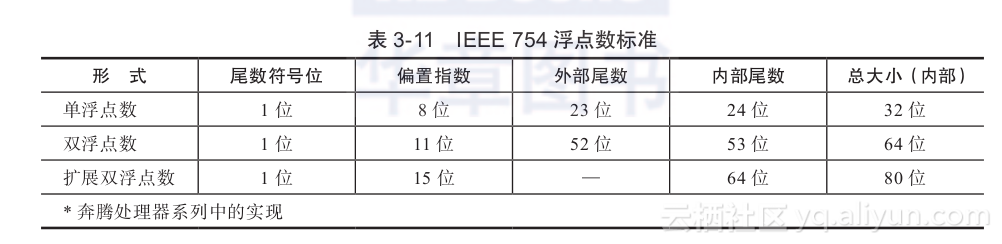

IEEE 754标准[3]包含了三种浮点数表示方法,分别为单浮点数、双浮点数和扩展双浮点数。表3-11列出了每一种表示方法的指数和分数范围。单浮点数和双浮点数在存储器或者外存中尾数分别是23和52位,在寄存器或者内存中,尾数分别为24和53位。扩展双浮点数表示方法有64位尾数且用于增加浮点数算法的精确度。尾数一般用带符号的量级数字表示,拥有独立的符号位。在存储器或者外存中没有扩展双浮点数的表示方法。

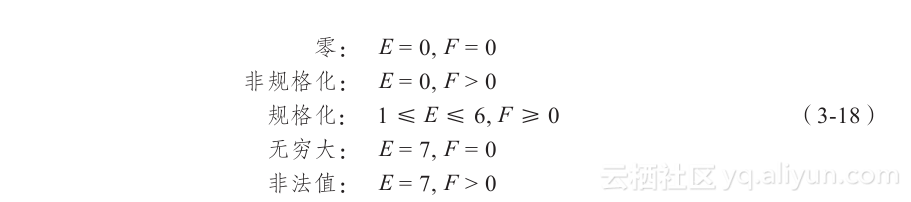

此外,IEEE标准将浮点数分为5个数据类,单数据类列出如下:

0

23位非规格化尾数

24位规格化尾数(只有23位可以储存在存储器中)

无穷大

NaN(不是一个数),表示一个非法的浮点数或者操作

公式(3-17)表示了非偏置指数e和偏置指数E之间的关系。单浮点数或者双浮点数的表示形式为1.F×2E,在小数点前有一个固定的1;然而,这个1没有被存储在存储器里。F是一个外部(存储器)尾数,而1.F是一个内部(寄存器)尾数。一个非规格化浮点数被定义为0.F×2E,有一个固定的0在小数点前。

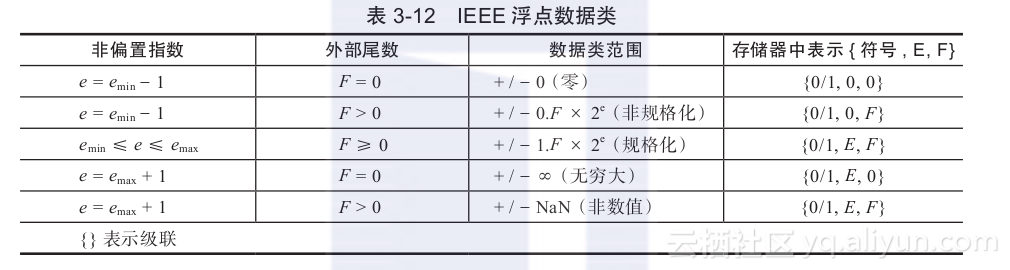

表3-12展示了每一种数据类的表示范围。在表中,emin和emax表示规格化浮点数的真正(非偏移量)指数范围。

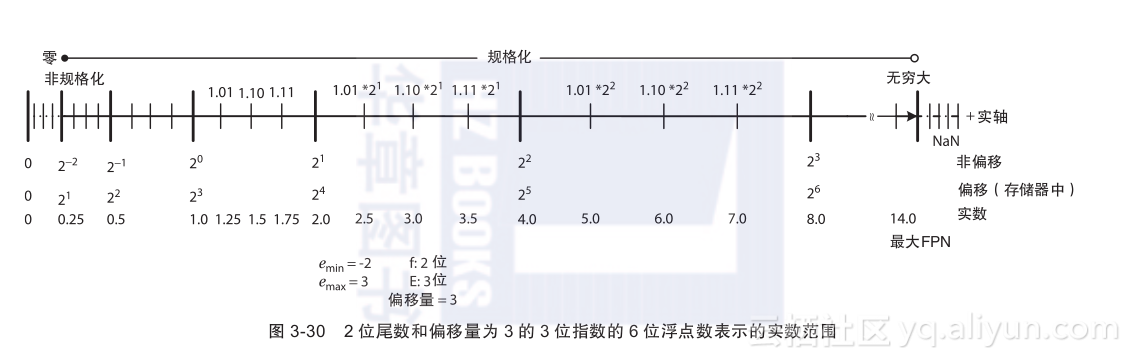

例如,假设偏移量为3的3位偏置指数,公式(3-18)定义了每一种数据类的E和F值。

3.8.2 浮点数据空间

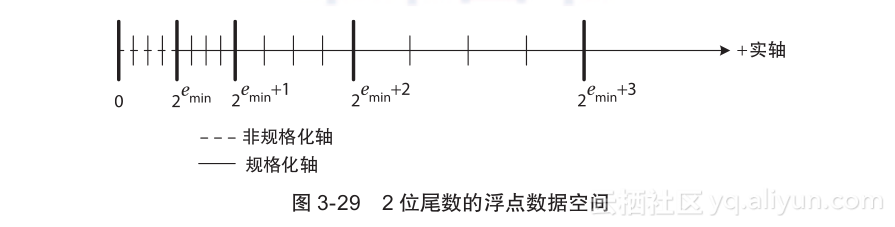

一个浮点数据空间可以用计算机系统中浮点数能表示的实数范围表示。图3-29展示了用正实轴表示的浮点数据空间。0和2emin(不包括0和2emin)之间的水平虚线表示非规格化数据空间。细线和粗线表示当尾数只有2位时用浮点数表示的特殊实数。在表示法中浮点数更多的位数意味着可以表示更多的实数。

例如,在单浮点表示法中,偏移量为127时,8位非偏置指数的范围是从emin = - 126到emax = 127。每一个尾数为23位。其数据空间在每一对粗线之间有222 - 1条细线。双浮点数据空间在每一对粗线中有252 - 1条细线。

图3-30展示了可以表示为有1位符号位,2位尾数和偏移量为3的3位指数的6位浮点数的正实数。如图所示,17个实数范围从0.25~14.0(包括)可以表示为6位浮点数形式。从0~0.25(不包括)的浮点数会被认为是非规格化的。

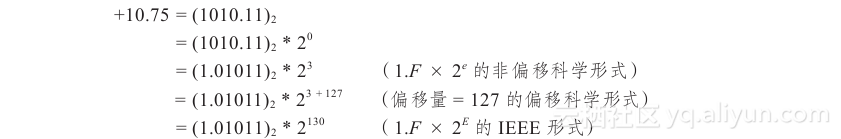

例3-8? 给出实数+ 10.75的对应的外部(存储器)单浮点数表示形式。

解:首先,将数值转换成二进制形式。然后将其表示形式转换为科学表示形式。

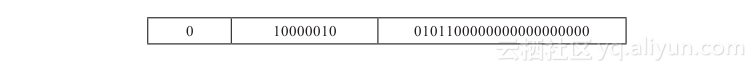

结果为如下的32位数,由一位符号位= 0, 8位偏置指数E = 130 = (10000010)2和23位尾数= (010110…0)2表示的数值:

或者写成十六进制:0x412C0000。1.F中的1没有被存储至存储器中。

除了符号位,浮点数的正数和负数的表示方法是一样的。负浮点数的符号位为1。例如,- 10.75在存储器中单浮点数表示为0xC12C0000。

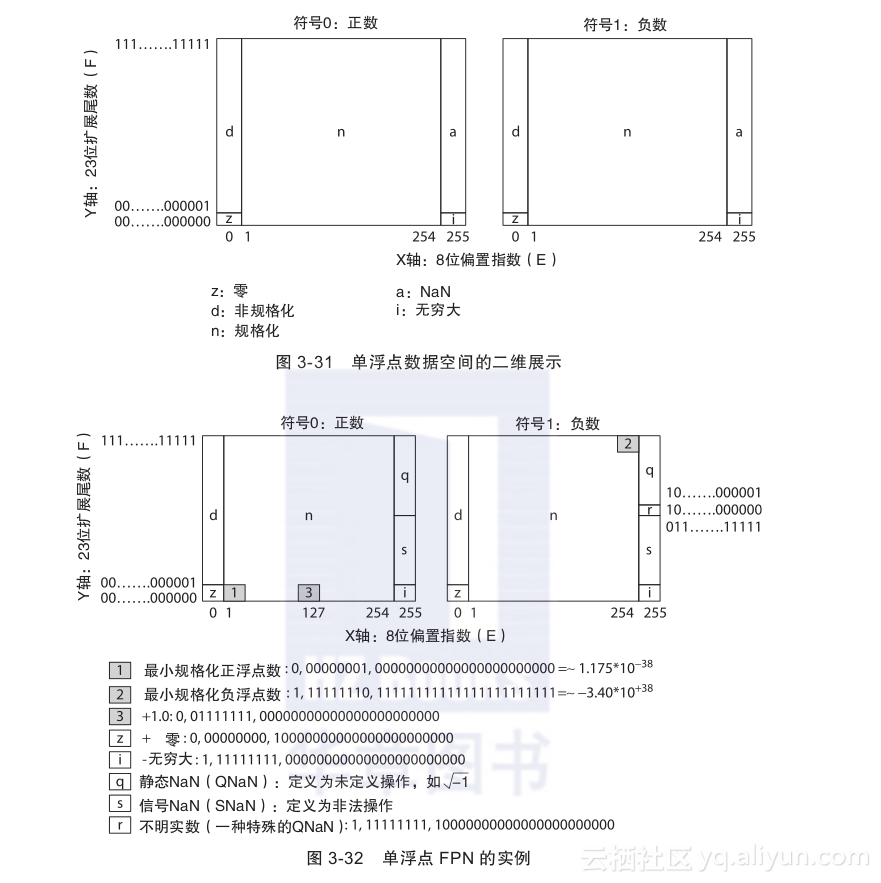

二维展示

表示浮点数据空间的另一种方法是用矩形域表示[4],如图3-31所示,表示的是单浮点数。两个分开的二维表示用于分别表示正浮点数和负浮点数的数据空间。在图中,x轴上的任意点表示指数值,而y轴上的点表示尾数值。两轴的数据范围不相同。

和图3-29中的一维表示相比,二维表示更容易定位一个特定浮点数的位置,或者一个浮点函数的定义域和值域,例如余弦值。例如,余弦函数的值域范围是0~1.0之间包括0和1.0所有可表示的浮点值。例如,函数的定义域和值域可能用于生成FPU的测试向量[4]。图3-32展示了在二维浮点数据空间中一些示例浮点值的位置。

最小的正规格化浮点值在图中被标记为第一项且位置在正规格化空间的左下角,其E = 1且F = 0。最小的(例如最大级)负规格化浮点数被标记为第二项且位置在负规格化空间的右上角,其E = 254且F为全1,即255。 + 1.0被标记为第三项且其位置在+规格化空间的最下方,其E = 127且F=0。±零其E = 0且F = 0。±无穷大其E = 255且F = 0。而且在Intel奔腾处理器系列中,有一些其他特殊的浮点数,例如NaN(QNaN)表示一个非法操作数——例如,- 1的开方——或者信号NaN(SNAN)表示一个非法操作[5]。

双浮点数据空间的二维展示也是类似的,除了用于表示指数和尾数数字的位数不一样以外,在双浮点数据空间中,指数为11位,尾数为52位。

3.8.3 浮点运算

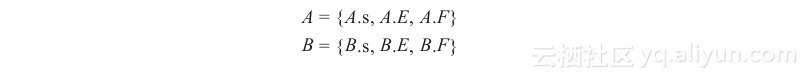

一个浮点数的指数和尾数分别都是整数且在浮点运算中可以分别操作。例如,两个实数0.1075 (10.75×10- 2)和72.5 (0.725×102)进行相加,更小的尾数将右移小数点,使得小数点对齐,进而得出两数之和72.5075(0.725075×102)。较小尾数移动的位数取决于两个指数。两个二进制实数相加的算法和十进制是相同的,将在以下列出。标记A.s和B.s,A.E和B.E, A.F和B.F分别表示两个浮点数A和B的符号位、偏置指数值和外部(存储器中)尾数值,即

这里{}用于表示级联

浮点加法算法:规格化数据空间

1)将输入初始化:A必须大于等于B。

i.将A. = {1, A.F}和B. = {1, B.F}转换为内部(内存中)尾数表示。

ii.保证|A|≥|B|。如果|A| < |B|,将A、B值交换;|X|表示X的绝对值。

2)对齐小数点:将B. 右移D位。D的定义如下。

i.让D = A.E - B.E。

ii.将B. 右移D位,左边用0填充。

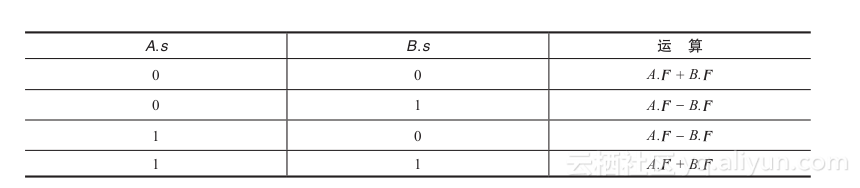

3)生成结果(R):计算R. = A. ± B. 。

i.生成R. ,作为A. 与B. 的和或差,根据以下A.s与B.s的值判断进行的操作:

ii.让R.s = A.s且R.E = A.E。

4)将结果规格化:如果R.未规格化,将R.转换为1.F的形式。

i.如果R.的形式为1x.F,这里x在3.i步中不是0就是1,这样R.E加1且R.右移一位,得到1.F形式;1x.F的LSB(最低有效位)将丢失。

ii.或者,如果3.i步中R.有前导零,则R.每左移一位就将R.E减1,为了消除前导零,将R.转换为1.F的形式。例如,如果R. = 0.01xxxxxx…x,则将左移两位变为1.xxx…x(1.F形式)。在这个例子中,R.E必须减2。

5)将结果四舍五入:

最终的结果,S. = {1, S.F},较高位将从R.中选择相应的位数:内部表示中单浮点数为24位,双浮点数为54位。舍去R.未使用的较低位。然而,舍去的位数可以用于四舍五入,可能会导致在S.的最低有效位上加1。如果四舍五入后的S.又变成了1x.F,那么需要重新将其规格化为1.F的形式。对于四舍五入更完整的讨论还应包括在IEEE浮点标准中列出的guard (G)、round (R)和sticky (S)等位,但已超出了本书涵盖的范围。

6)最终输出:

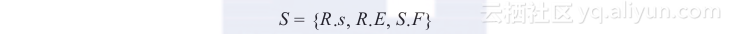

在存入内存之前,R.s、R.E和S.F将连接成32位单浮点数或者64位双浮点数,即

在上千万个运算中,R.为64位,且所有整数运算和位移函数都可以用于64位尾数中来将四舍五入错误减少到最小值。

例3-9? A = 17.875且B = 15.75,计算S = A + B。假设A、B和S都为具有1位符号位、偏移量= 63的7位e指数和8位尾数的16位浮点数。

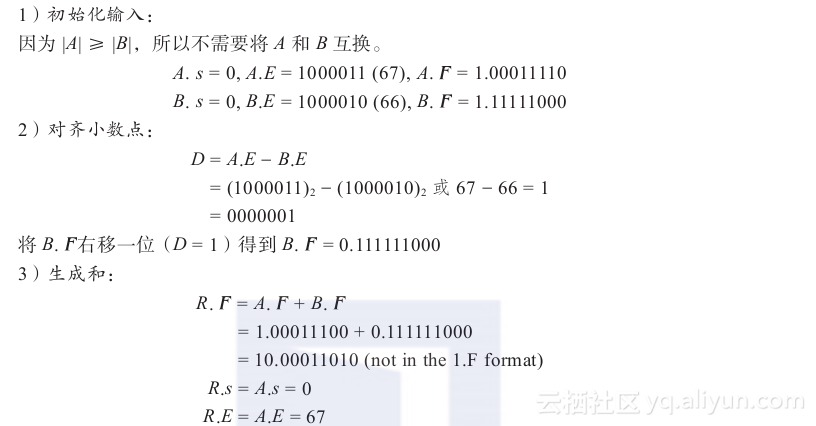

解:计算S = A + B的5个步骤如下:

1)将实数A和B转换为二进制表示法。

2)将二进制表示法转换为与其等价的非偏置指数科学形式。

3)将非偏置指数科学形式转换为与其等价的偏置指数形式。

4)将偏置指数形式转换为16位内存表示形式。

5)遵循浮点加法算法,将两个浮点数相加。

步骤1:转换为二进制

A = 10001.111 × 20 B = 1111.11 × 20

步骤2:科学形式(非偏置指数):

A = 1.0001111 × 24 B = 1.11111 × 23

步骤3:科学形式(偏置指数),IEEE形式为1.F × 2E

A = 1.0001111 × 24 + 63 B = 1.11111 × 23 + 63

A = 1.0001111 × 267 B = 1.11111 × 266

步骤4:内存中表示形式:

A = 0x431E (0, 1000011, 00011110) B = 0x42F8 (0, 1000010, 11111000)

步骤5:运用之前讨论的浮点加法算法:

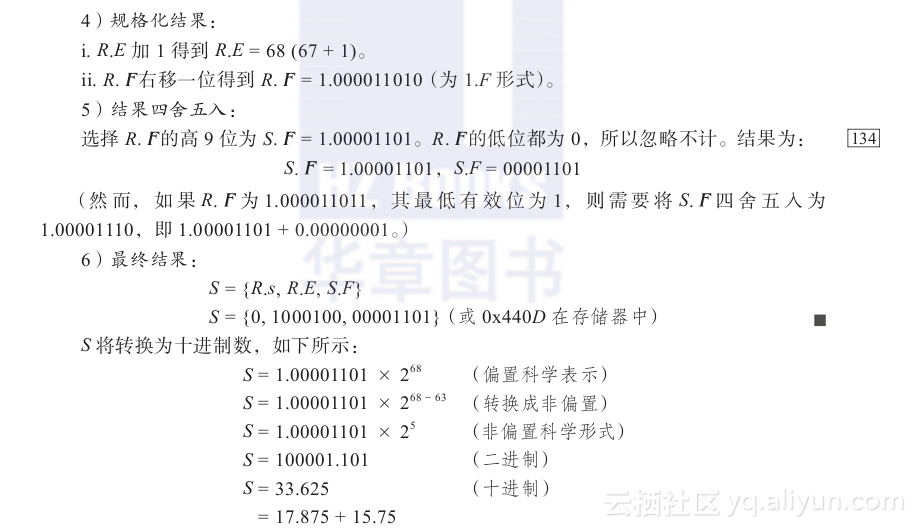

S将转换为十进制数,如下所示:

浮点减法、乘法和除法都是类似的过程。对于减法,尾数先对齐,与加法中一样,然后如果A.s = B.s则相减,A.s ≠ B.s则相加。对于乘法,尾数相乘,指数相加,且符号位进行异或运算。最后,对于除法,尾数进行整数除法,指数相减,符号位进行异或运算。四舍五入和规格化步骤与之前讨论的浮点数相加步骤相同。

然而,因为对于浮点数除法,被除数的内部尾数N.和除数的内部尾数D.最高有效位都为1,N.不用在左侧补零,如图3-28所示的整数除法(参考练习3.29)。

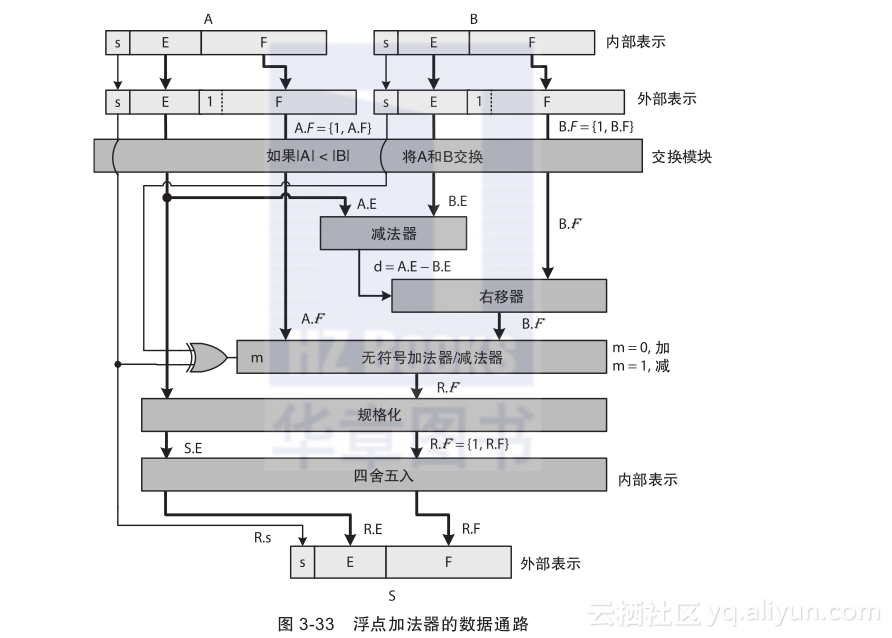

3.8.4 浮点单元

图3-33展示了浮点加法器的数据通路。数据通路包括实现算法中每一步骤的组合电路模型。在数据通路中,如果|A| < |B|则会用到交换模块。为了保证|A|小于|B|,A.E必须小于B.E,或者如果A.E = B.E,A.必须小于B.。交换模块(未展示)中的两个减法模块生成A.E - B.E和A. - B.的差值。这两个模块的借位信号表示|A|≥|B|是否为真。

如果|A| < |B|,则A和B必须进行交换,A为较大的数,为数据通路左边的输入。两个2-1的MUX(未展示)在需要时转换将A转换为B或者将B转换为A。如果A.E < B.E或者当A.E = B.E且A.F < B.F时,A和B两个输出需要进行转换。

在计算A. ± B.时,右移模块用于调整小数点的位置。位移模块也用于每一个的规格化和四舍五入模块。组合位移将在后续讨论。

组合位移

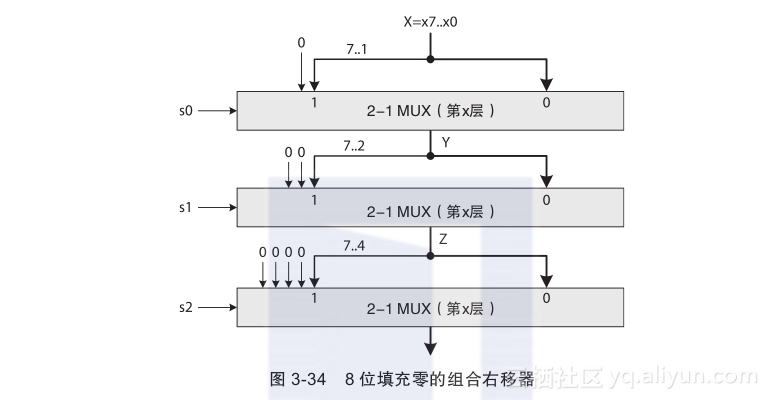

组合位移器用log2 (k)个2-1 MUX实现,组织成log2 (k)层次,其中k表示数字需要移动的范围。例如,对于k = 8,组合位移其可以将输入右移0~k - 1位或者7位。图3-34展示了k = 8的8位组合右移器。3位S = s2s1s0可以移动的范围是0~7位。s2、s1和s0为三个MUX的输入。

如图所示,当s0 = 0时,最高层(第0层)MUX选择X作为输出,当s0 = 1时,选择X右移一位作为输出。当s1 = 0时,下一个MUX选择Y作为输出,当s1 = 1时,选择Y右移两位作为输出。例如,当s2 = 0时,最后最底层(第2层)MUX选择Z作为输出,当s2 = 1时,选择Z右移4位作为输出作为输出。

例如,当S=s2 s1 s0 = (011)2时,s0 = 1使得第0层的MUX将右移一位输出。信号s1 = 1使得第1层将Y右移两位作为输出。最后s2 = 0使得第2层MUX输出Z本身数值。作为结果,位移器将X右移了3位,当S = (101)2时,X将右移5次。当S = (111)2时,X可右移的最大次数为7次。