3.7 设计实例

作为之前讨论的实现整数加法和减法操作组合电路的补充,以下小节将介绍组合整数乘法和除法电路。乘法的基本操作为加法,除法的基本操作为减法。然而,一些乘法和除法算法会同时用到加法和减法。同时使用加法和减法操作的2的补码乘法器将在第6章进行介绍。

3.7.1 乘法器

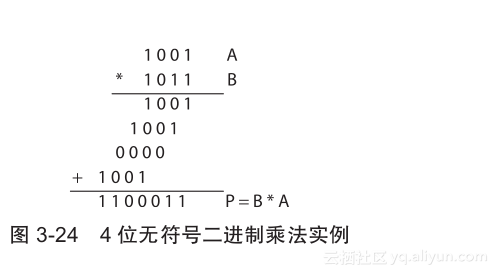

图3-24展示了4位无符号乘数B = b3b2b1b0和4位无符号被乘数A = a3a2a1a0的乘法过程。乘法过程的每一步产生一个加数。在图中,(1001)2、(1001)2、(0000)2和(1001)2是产生的4个加数,分别由b0、b1、b2和b3和A相与产生的。每一个新产生的加数会左移k - 1次,k代表乘法的步数。如图所示,4个加数在相加产生最终的乘积P之前都被分别按顺序左移0、1、2和3位。

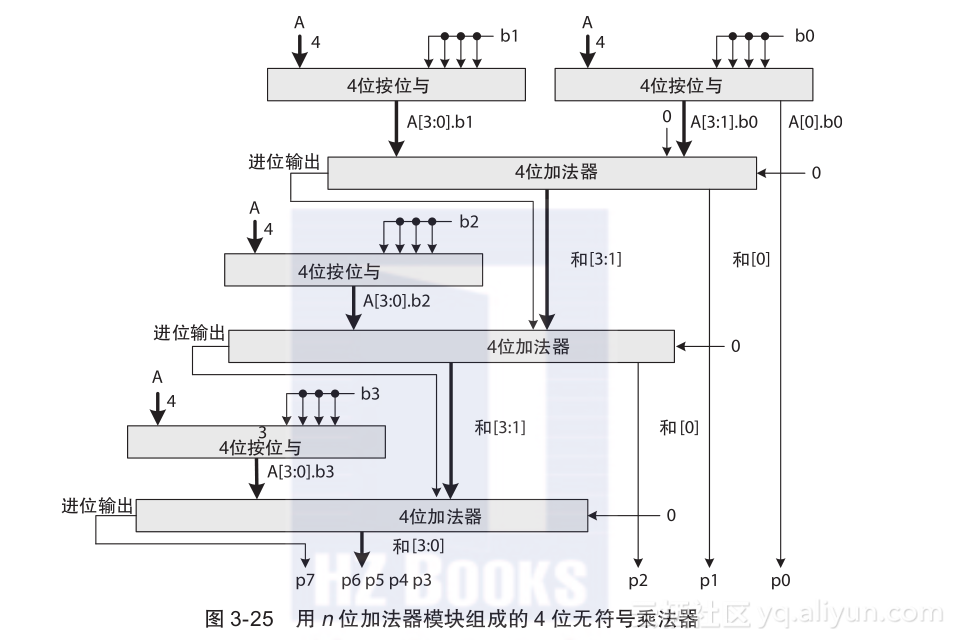

例如图3-25所示的n = 4乘法过程,设计组合n位乘法器电路的一种方法是用n - 1个n位加法器和n个n位按位与模块组成。这个设计很直观且是基于图3-24所示的步骤进行的。但是这种设计有较长的传输延迟因为除了前两个加数,其他的加数每次都只加一个,这样会造成很长的从输入到输出的信号路径。

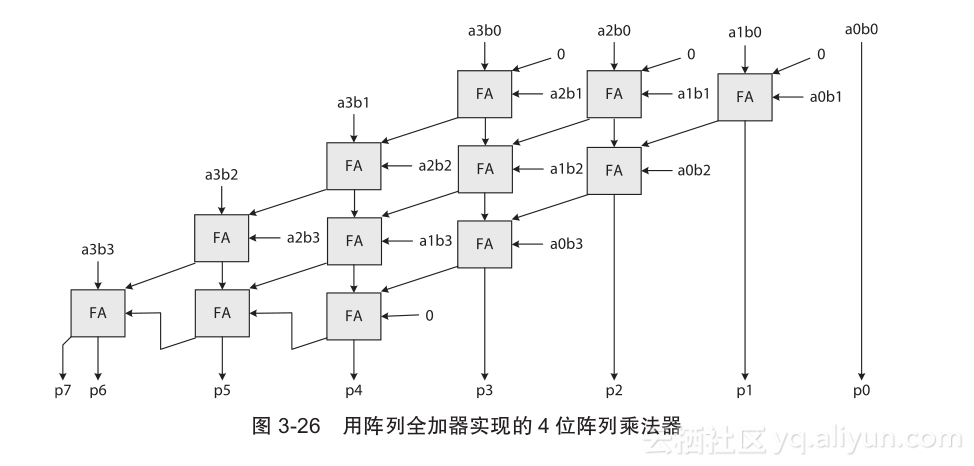

或者我们可以使用全加器片来对加数进行加法操作,每一次操作一列。当全加器连接在一起时,就产生了一种叫作阵列乘法器的二维结构。图3-26展示了一个用6列全加器实现的4位阵列乘法器。加数的和值每一次都能够确定一列,有点类似于多个加数的手工加法。在图中,一个加数用其独立的位,如aibj表示,这里ai表示被乘数A的第i位,bj表示乘数B的第j位。乘积的每一位都是一位由全加器链在列中产生的最终和。在每一列中,没有用到的输入将连接到0上。最后一位乘积位p7等于全加器列的进位输出位。

在图中,最后一行的全加器组成了一个CPA,CPA可以用CLA加法器代替从而将乘法器的总传输延迟降到最小。

3.7.2 除法器

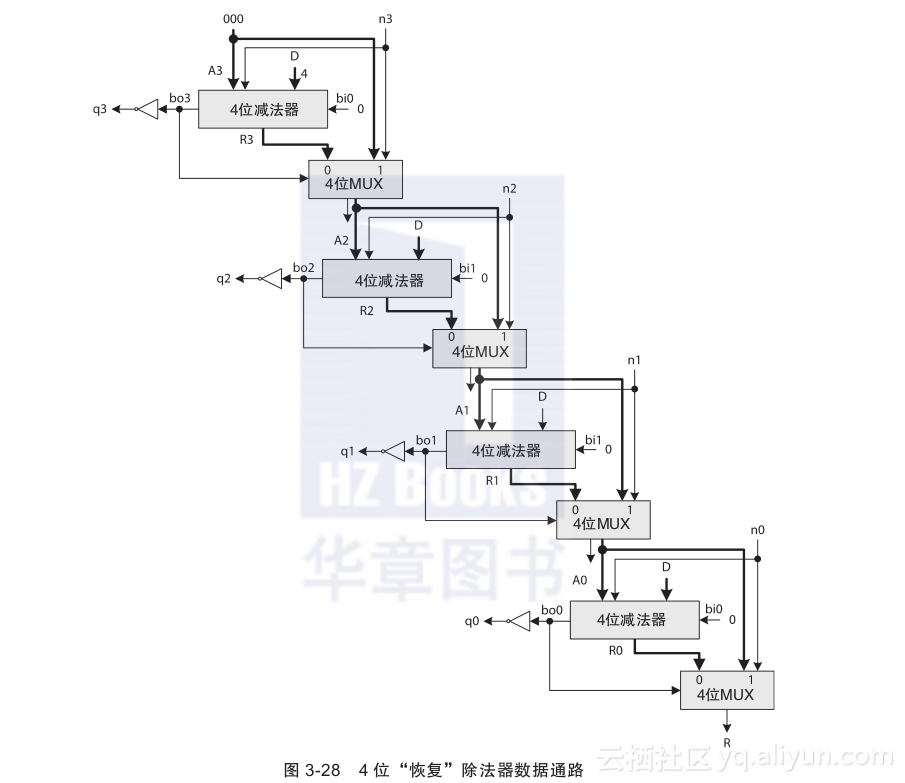

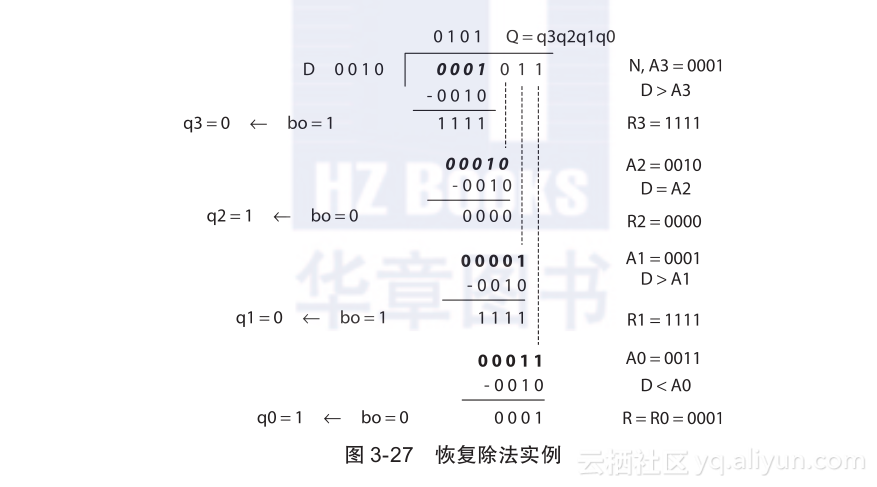

图3-27展示了用一个4位无符号被除数(分子)N = n3n2n1n0 = 4’b1011除以4位除数(分母)D = 4’b0010产生4位商Q = q3q2q1q0 = 4’b0101和4位余数R = 4’b0001的除法过程。N被从左填充n - 1个0,在这个例子中为3个0;即最开始的被除数为{000, N},这里的{}用于表明为串联。在每一个步骤中,除数D将被被除数较高的n位减去,在除法的第k步中定义为Ak。如果D≤Ak,对应的商位为1;否则商位为0。

图中所示的除法步骤也被称为恢复除法算法,因为每一次当Ak < D时(例如,A3 = 4’b0001 < D = 4’b0010),Ak - D < 0,这样Ak,不是余数Rk = Ak - D用于下一步除法的开始,即为“恢复”。在这个例子中, Ak较低的n - 1位与N的下一位连接组成下一个n位被除数Ak - 1。需要特别指出的是,对于n = 4,如图所示的{000, N}除以D的除法步骤和产生4位Q和4位R的步骤如下所示:

1)R3 = A3 - D (4’b0001 - 4’b0010 = 4’1111)产生R3 = - 1,且借位输出为1(例如bo3 = 1)、q3 = 0。

2)R2 = A2 - D (4’b0010 - 4’b0010)产生R2 = 0,且bo2 = 0、q2 = 1。

3)R1 = A1 - D (4’b0001 - 4’b0010)产生R1 = - 1,且bo1 = 1、q1 = 0。

4)R0 = A0 - D (4’b0011 - 4’b0010)产生R0 = 1,且bo0 = 0、q0 = 1。最终的余数R0 = 4’b0001。

图3-28展示了4位位并行恢复除法的数据通路。在除法的每一步中都需要用到一个减法器、一个非门和一个MUX。减法器计算Rk = Ak - D并产生bok。非门产生商位,例如qk = bok。MUX用于用qk位选择Ak或者Rk。公式(3-16)估计了每一步除法的传输延迟。

Δdivision - step=Δsubtractor + ΔMUX(3-16)阵列除法器,类似于一个阵列乘法器,可以用一个1位除法片阵列来组成。每一片将完成一个组合减法器MUX的功能。组合起来的功能可以翻译为最小SOP或者POS表达式的真值表(更多细节参照练习部分)。

对于很大的n,一个算术功能设计为一个组合电路需要相当多的逻辑门来实现。当算法是重复的并且可以替代地重复实施时更是如此,例如乘法器和除法器。例如,除了用4个减法器、4个MUX和4个非门来实现如图3-28所示的4位恢复除法器,我们也可以用一个减法器、一个MUX、一个非门和一系列的寄存器来产生4步除法中的4个商值。每一步除法的结果都存在寄存器中。然而,一个硬件模块重复使用需要一些额外的硬件来控制每一步的时序,且会稍微增加获得最后结果的总时间。这个设计将在第6章中进行讨论。