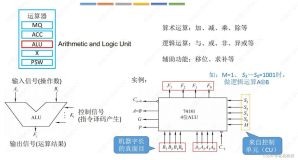

3.5 2的补码加法/减法器

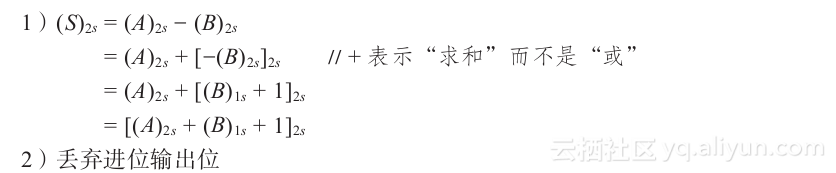

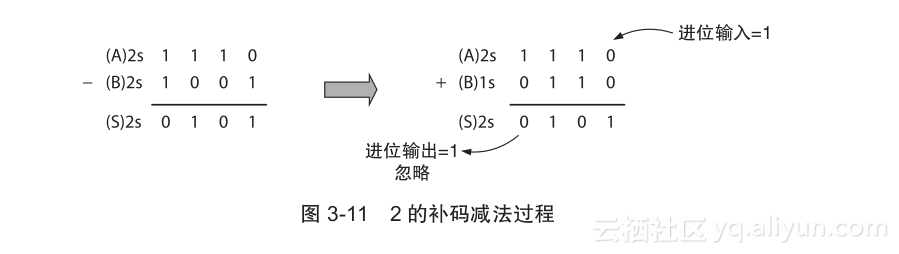

对于带符号的算术运算,它们的数值可以表示成正数或者负数的2的补码。两个n位数字(A)2s和(B)2s的减法可以表示成(A)2s和(- B)2s的加法,如下所示,这里(B)1s表示简单地对B的每一位进行取反,即B的反码。

2的补码减法算法

图3-11展示了2的补码减法算法过程。“+ 1”用一位进位输入来实现。

类似地,下列算法描述了n位2的补码加法。在这个例子中,输入B没有变化且进位输入设为0。

2的补码加法算法

2的补码算术产生n位2的补码输出,进位输出被忽略且不被计算到最后结果中。然而,结果还是有可能会溢出。例如,考虑用1减最小的n位二进制补码负数,或者1加上最大的n位2的补码正数。在两个例子中,结果差值和和值都会超过n位负数和n位正数2的补码表示的范围。

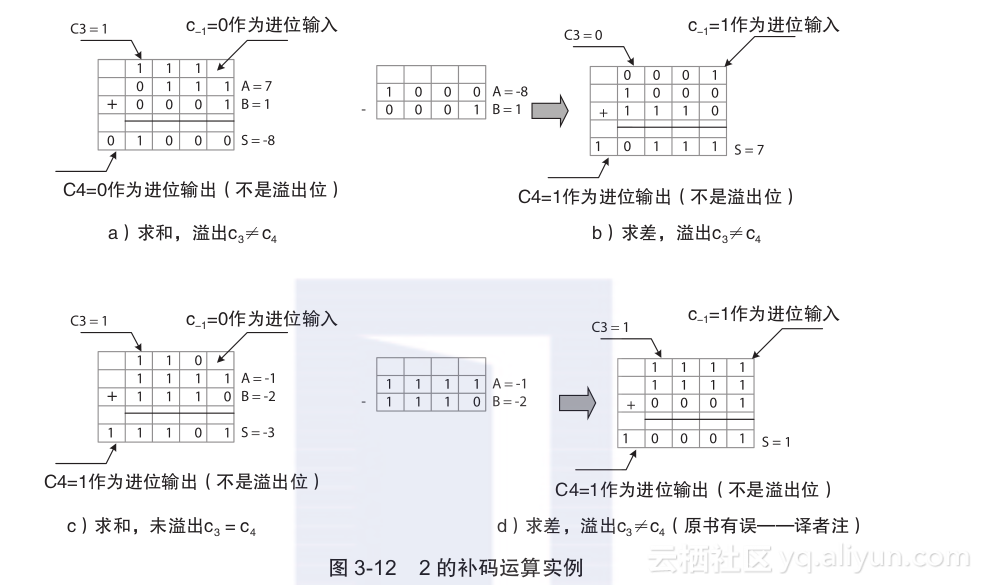

当A和B都是2的补码正数时,它们的符号位为0。在这个例子中,为了保证A + B不会溢出,加到符号位的进位必须为0。这样会产生0作为进位输出;不然就会产生溢出。例如,考虑图3-12中的例子a和c。在例子a中,A = (0111)2s = 7且B = (0001)2s = 1都是2的补码正数,此外,A是最大的4位正数。如图中所示,当B = 1与A = 7相加,结果为(1000)2s = - 8,一个负数,这就意味着溢出。在这个例子中,c3 = 1,且当其与都为0的符号位相加的时候,这就让符号位之和变为1(负数)且c4 = 0≠c3 = 1。要使溢出情况不会出现,当两个2的补码正数相加时,c3和c4都必须为0。

在例子c中,当两个负数A = - 1和B = - 2相加,符号位都为1,如果c3 = 1产生c4 = 1

则A + B不会溢出。否则,结果就会溢出,生成一个正数为结果。从例子a和例子c中得到的结论是当c3 = c4时,结果不会溢出,不论A和B是正数还是负数的2的补码形式。

例子b和d展示了减法。在这个例子中,等式A - B就是在计算A + (B)1s + 1。在例子b中,当B = 1(正数)去减A = - 8时(最小的4位2的补码负数),c3为0,加到符号位(都为1)上时,产生7为结果(不正确的结果)。注意,c4 = 1≠c3 = 0。在例子d中,A = - 1和B = - 2都为2的补码负数,且当相减时,结果不会溢出。注意到在这个例子中,c3 = 1与c4 = 1(c3 = c4)值相等。两个正数相减也不会产生溢出的情况。

表3-2为n位2的补码加法器/减法器溢出信号ovf的真值表。进位cn - 2与符号位相加产生最终进位cn - 1。公式(3-14)定义了溢出信号:

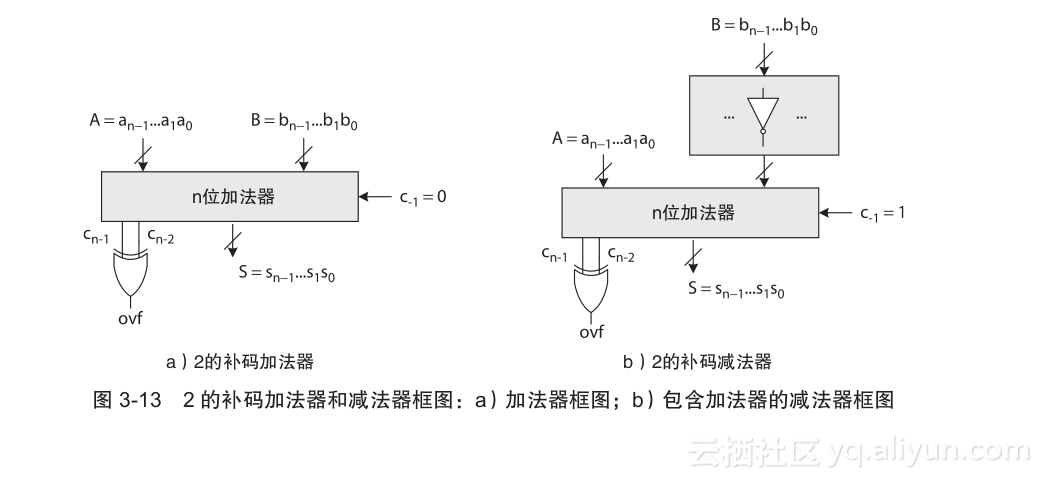

图3-13展示了两个框图:a)2的补码加法器和b)2的补码加法器。两个框图只有输入(B)2s和处理进位不相同。在图3-13a中,输入B与A相加,并没有改变表示形式。在图3-13b中,输入B在与A相加之前,经过了按位非运算。这样,我们可以只有一个加法器模块来组合两个电路框图实现一个加法器/减法器模块。可以用反相器模块来转换结果,当加法时输出B,当减法时输出B的非,当运算减法时,E = en - 1…e1e0等于B的反码或者表示为(B)1s。模式信号m用来表示运算模式,当m = 0(进位输入为0)时,运行加法,当m = 1(进位输入为1),运行减法。

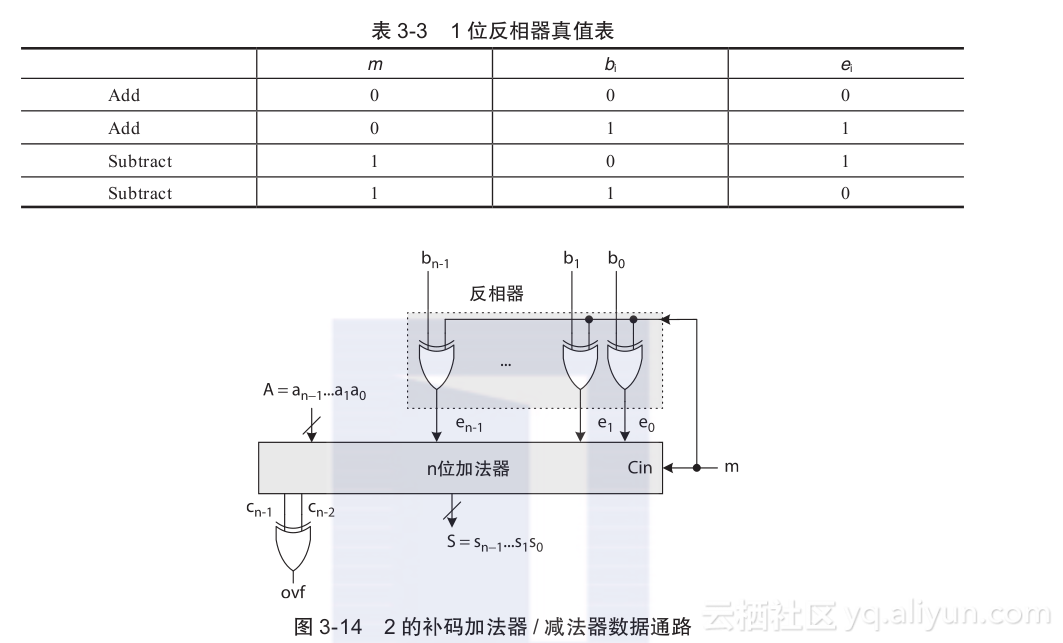

表3-3为一位反相器片的真值表。最后组合设计如图3-14所示,信号m也被用于最初的进位输入值。注意到有信号m的模块与进位输入连接不能用于这几位串行的大型加法器/减法器电路。如果需要设计位串行电路,必须用分开的进位输入作为输入。