第3章

Digital Logic Design and Computer Organization with Computer Architecture for Security

组合电路:大型设计

3.1 简介

在前一章中介绍的设计技术只适用于很少输入数目的组合电路。有很多输入的组合电路必须以不同的方式设计。例如,考虑有n = 32个输入的组合电路。其真值表可能会有超过40亿行——对于第2章介绍的设计电路方法来说,这个数目特别巨大。再有,大型电路肯定会遇到设计扇入和扇出的需求。这就要求一种自顶向下的方法,将大型组合电路设计问题反复地分成较小的问题,直至小到可以用第2章所学的设计技术来解决为止。然后大型电路通过将较小型电路模块进行组装来设计完成。

具有加法、减法、乘法和除法等初级算术操作的电路是大型电路应用于处理器的例子。类似于软件解决方案可以实现需要不同处理器时间和存储器使用情况的代替算法,大型组合电路可以用不同总量的硬件实现(例如三极管数量)。具有越多的三极管数量的电路解决方案,通常意味着具有更小的电路延迟来执行更高数量的逻辑操作,但也更耗能量。

通常,更多的硬件意味着更少的处理时间。包含快速算法模块的CPU有望更快地运行;多核处理器有望比单核处理器运行任务速度更快,等等。

在这章中,我们提供了算术电路的设计实例。特别地,我们将讨论通常称为快速加法器的设计,也展示减法器、2的补码加法器、算术逻辑单元(ALU)、乘法器和除法器的设计。这章同样也会展示IEEE浮点(FP)数标准和算术。

自顶向下的设计方法

自顶向下的方法,也叫分层的方法,是指一种设计流程,如包含父结点和叶结点的树结构。在根结点的大型设计问题可以依次在叶结点划分为较小的设计问题。根结点的问题第一次将被分为较小设计问题为子结点。如果需要,在每一个子结点(现在为父结点)上的较小设计问题又可以分为更小的设计问题。这个处理过程一直持续直到每一个在叶结点的设计问题足够小并且拥有更少的输入。

对于叶结点上的每一个设计问题,第2章中的技术都可以用来设计电路。这些电路随后将连续组合成目标大型组合电路。设计可能需要一个或多个较小电路的副本。最终电路必须无任何扇入和扇出问题。

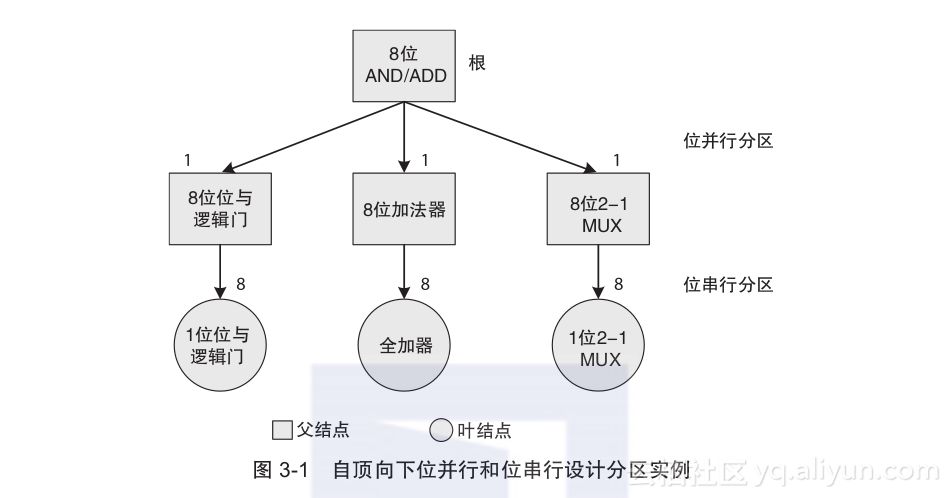

在设计流程中的每一步,有很多种方法和算法都会进行检查,对如电路延迟和逻辑门数量进行权衡分析,然后选出最佳的解决方案来满足整个设计要求。通常,一位并行和一位串行设计分区技术(稍后定义)从根结点开始被用于每一个父结点。

当设计问题被分成较小的设计问题时,分区被称为位并行的。例如,生成n位与或者n位和的组合AND/ADD电路模块的设计可以视为三个分开的设计问题:n位的位与逻辑、n位的加法器和n位2-1的多路选择器(MUX),当n = 8时如图3-1所示。MUX选择位与逻辑的结果或者加法器的和值来作为输出。虽然位与逻辑、加法器和MUX都只是实现单一的功能,但是对于第2章所学的方法来说,还是很大型的设计问题。这三个模块都必须再分为更小的设计问题。

位串行方法用于将设计问题分成有更少输入的较小问题。例如,n位输入的大型电路设计问题可以分为称为片的k位输入设计问题,这里k(最好)能整除n。每片都可以执行一个或者多个函数操作,但只能对较少的输入位进行操作。例如,一个8位加法器可以用8个全加器(FA)进行设计;8位2-1 MUX可以用8个1位2-1 MUX进行设计。在图中,每个结点旁边的数字表示了片的数量。在k位片不会违反所用逻辑门的扇入扇出限制时,常数k可以作为一个选择。

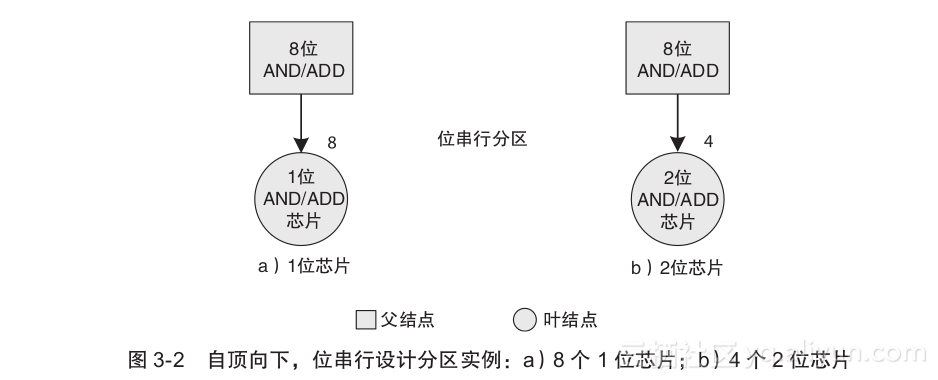

在用位串行方法设计8位AND/ADD模块时,我们可以使用8片1位AND/ADD片或者4片2位AND/ADD片来进行设计,如图3-2所示。通常n位模块可以用n个1位、n/2个2位、n/4个4位等来设计。每片需要输出附加信号——例如,当选择加法函数时,连接片所需要的进位输出位。为了保证最小传输延迟,位串行可以被用真值表和其他设计方式化简成SOP或者POS表达式进行模块化。

使用位并行还是位串行方法,在每一步的使用中都会对结果电路的最大传输延迟和所需逻辑门数目造成影响。这一章展示了一些常见的大型组合电路。