2.9 实现

现代数字电路设计师依靠CAD工具来将设计模型翻译成实现数据。数字设计CAD工具将数字电路的描述综合(翻译)成优化过和对技术依赖的门级描述,称为网表。特定用途的集成芯片(ASIC)和FPGA都是非定制IC技术的例子。处理器芯片是典型的定制IC技术的例子。电路可以用框图表示,也可以用HDL语言描述,或者同时使用这两种方法描述。然而,现代CAD工具需要将电路描述成HDL语言。

2.9.1 可编程逻辑器件

可编程逻辑器件(PLD)是预制的,即不包含任何制造缺陷的封闭现成设备。它们可以被编程(例如配置)去实现网表,这个过程是立即实现的,有时甚至是动态的过程。简单可编程逻辑器件(SPLD)是所有可编程逻辑器件中最简单的一种。SPLD使用线逻辑来实现逻辑表达式,且通常用于实现小型数字电路。复杂可编程逻辑器件(CPLD)是通过芯片内部配置线通道来实现更复杂逻辑电路的下一代可编程逻辑器件。

我们在第1章中简要地讨论过,FPGA是一种包含若干可配置逻辑块(CLB)、可配置线通道和与芯片(I/O)引脚相连的可配置IO模块PLD的现代版本。FPGA可以看成是现代与TTL 7400芯片系列和电路板的等价。7400系列是第一代被用于一般用途的IC芯片。该系列包含了标准逻辑门和更大的一些组合逻辑模块,例如MUX、译码器和加法器,和一些用于设计时序电路的模块。在20世纪六七十年代,它们被用来设计小型和大型计算机。如今7400系列芯片有时会用于教学用途,特别是用在逻辑设计的引导课程中。

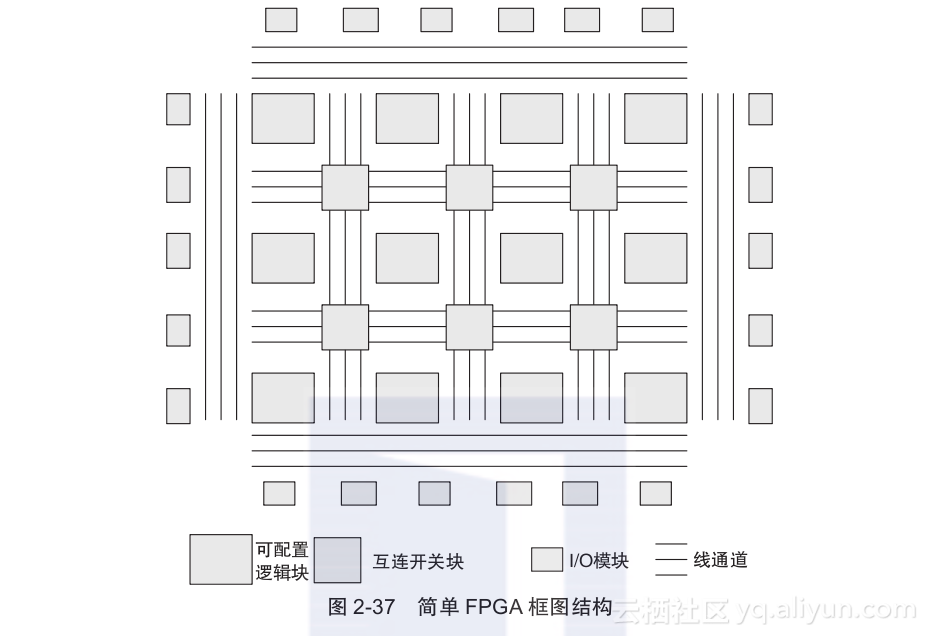

FPGA需要编程数据来配置和将用网表表示的CLB和I/O模块互连起来。一些I/O模块可配置成输入引脚和输出引脚。图2-37展示了包含9个可以实现一个或两个简单逻辑功能CLB的简单FPGA的内部构成。线通道和开关组用于每一个CLB输入和输出与其他CLB的互连,同时也将I/O模块与I/O引脚互连起来。

一些FPGA包含了配置存储器以根据需要实现不同的网表。现代FPGA通常包含上千个CLB,一些FPGA甚至会包含存储模块。还有一些片上系统(SoC)FPGA芯片[3-4]可以包含例如CPU和数字信号处理器(DSP)这样复杂的模块。对于这些芯片,我们可以更容易地不需要加工地设计定制和复杂的数字电路。Altera和Xilinx公司提供了带有通用串行总线(USB)接口的FPGA开发组件[3-5]。

2.9.2 设计流程

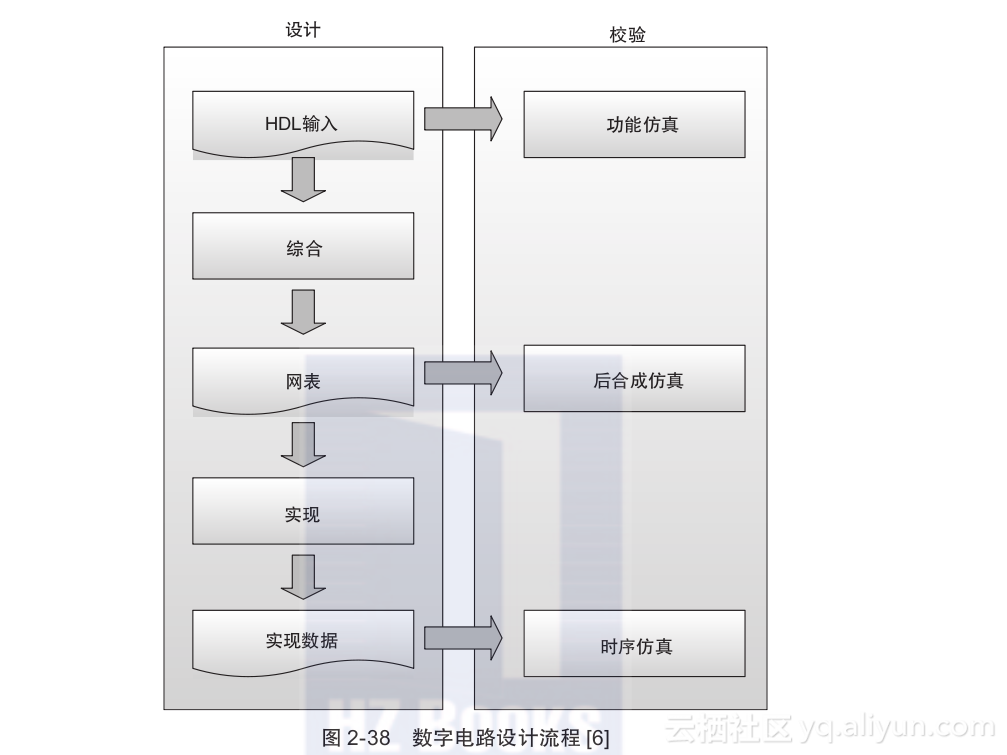

图2-38展示了数字电路的一般设计流程。设计流程一般包括设计输入、综合和实现阶段。设计流程里的每一个步骤会对目标电路产生一种不同的描述,其中每一个描述都会去验证设计是否有错误。

1.设计输入

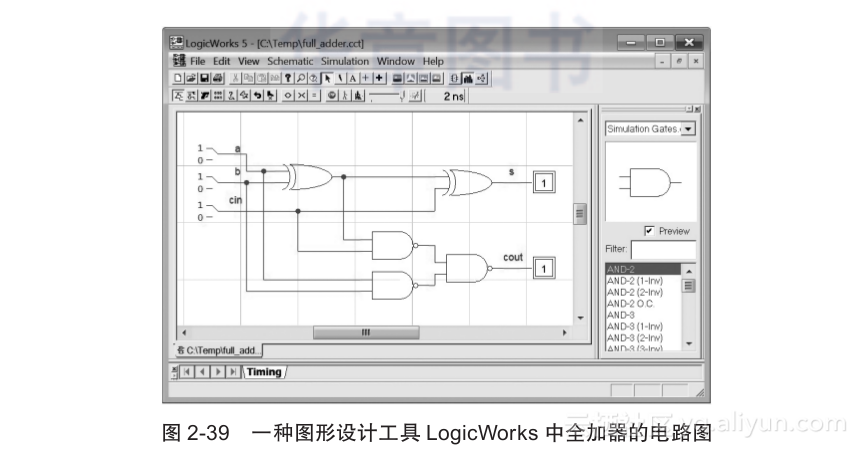

在设计的这个步骤中,目标数字电路将被手工地用图形设计工具、HDL或者两者共同去描述。在工业领域中,图形设计工具的严格使用许多年以来已逐渐减少,这有利于我们使用HDL。我们将会在2.10节讨论Verilog HDL。图2-39展示了用图形设计和一种叫LogicWorks的仿真工具来设计全加器的过程[7]。LogicWorks中没有合成工具。图形设计工具通常包含逻辑门库和一些常用的组合逻辑和时序逻辑电路模块。它也可以包含7400芯片系列的库。此外,图形设计工具可以包括混合设计输入功能来进入数据通路原理图,数据通路中的模块都是从库中选择或者用HDL设计的。

2.功能仿真

用图形和/或HDL来设计电路必须通过校验保证电路的运行符合预期。例如,给定输入,如图2-39所示的全加器的输出能符合全加器的真值表吗?因为这个校验过程,特别是对于大型的电路会消耗许多时间,所以校验过程通常被分为功能校验过程、合成后校验过程和时序校验过程。功能仿真只用于校验设计的正确性,并不关心其实现中的问题。这是保证设计正确的第一步。如果电路的功能仿真没有错误,则合成就将作为电路实现的第一步;然而,设计还可能会有合成错误或者时序错误。

3.合成后仿真

在合成步骤中,电路设计被解释为其对应的基于给定技术可用资源下的网表,例如给定的FPGA中每个CLB中可用的逻辑资源。每个CLB只能实现一些简单的逻辑表达式——例如,两个4变量的逻辑表达式。设计逻辑表达式需要把大的逻辑表达式分为较小的逻辑表达式——例如,不超过4变量的逻辑表达式。这个较小的逻辑表达式存储于电路网表中。

合成后仿真过程需要保证电路设计可以正确地翻译和其生成的网表必须正确地描述了目标电路。合成后仿真比时序仿真需要更少的处理时间。此外,一些延迟信息——例如,CLB信号传输延迟,可能会在合成后仿真中出现。

4.时序仿真

当网表映射到在计算机上模拟运行的目标设备中的可用资源之后,开始进行时序仿真。例如,用FPGA芯片的虚拟模型,网表通过一个叫布局布线的过程配置CLB、I/O模块和线通道。

在布局步骤中,网表中的最小表达式被分配到CLB,电路初级输入和输出信号通过I/O

模块被分配到I/O引脚。一些设计可能也需要复杂的模型——例如,已经存在在芯片上的CPU、DSP和存储器。

在布线的过程中,网表中的信号依赖信息通过在芯片上的线通道和开关组将不同CLB和I/O模块的信号连接起来。然而,布局和布线任务通常不是独立完成的;CLB上的逻辑表达式分配、I/O模块上的初始I/O信号都可以改变,这是为了:1)最大化地利用芯片上的可用资源;2)将传输延迟减到最小。时序仿真是用来保证设计时序需求。