2.8 设计实例

在第1章中讨论过,一个数据通路包括许多电路模块。本节我们将讨论一些常见的但是比较小型的组合电路模块。在第1章中图1-1中所示的“选择器”模块也被叫作多路转换器。其他将讨论的实例包括简单的加法器、译码器和编码器模块。

1位加法器,也叫作全加器(FA),产生两个1位输入的和,并输出一个0或1的传位进位。译码模块将数字A(0、1、2等)转换成对应的输出信号(例如,f0、f1、f2等)。任何时候都只有一个输出f0、f1等是有效的。另一方面,编码器所做的工作是译码器的逆向工作,将产生与输入信号对应的数字。这节中我们将讨论下列实例:

高电平信号FA设计实例。

1位2-1的多路选择器和1位4-1的多路选择器设计实例。

低电平输出信号的1-2译码器设计实例。

低电平输入信号的3-2编码器设计实例。

2.8.1 全加器

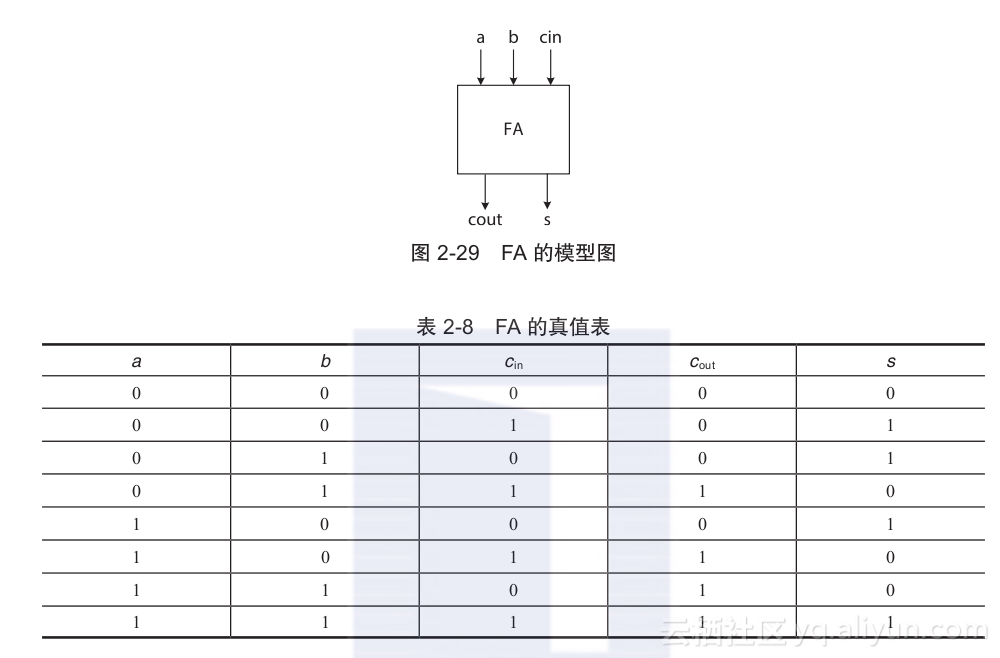

一个全加器有三个1位输入,其中一个输入是进位输入(cin),输出为一位和(s)和一位进位输出(cout),如图2-29所示。表2-8展示了全加器的真值表。在表中的每一种情况中,s和cout都由三位数据a、b和cin的和决定。多全加器模块可以用于设计大型加法器,这将在下一章中讨论。

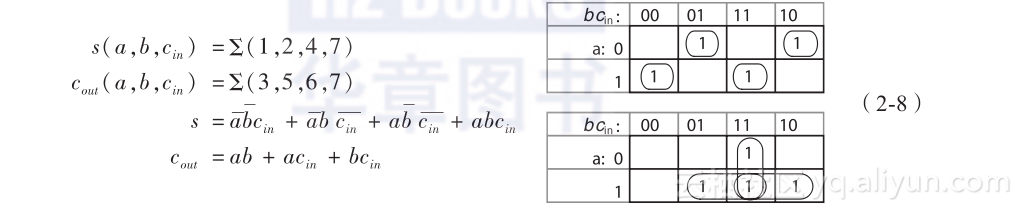

s和cout的最小SOP表达式如下求得:

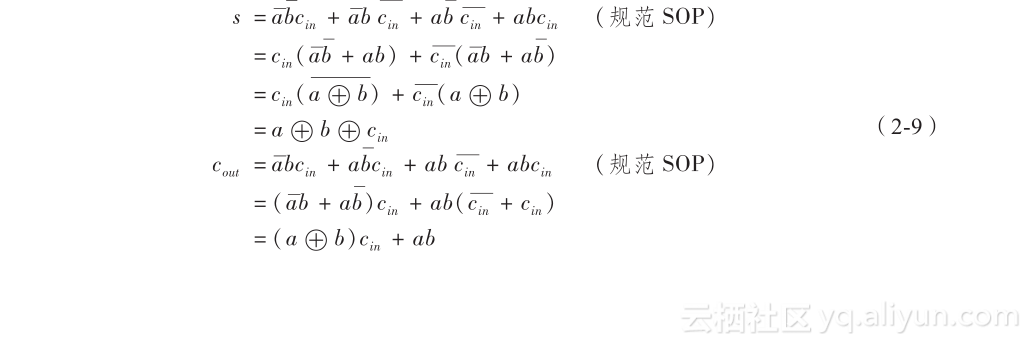

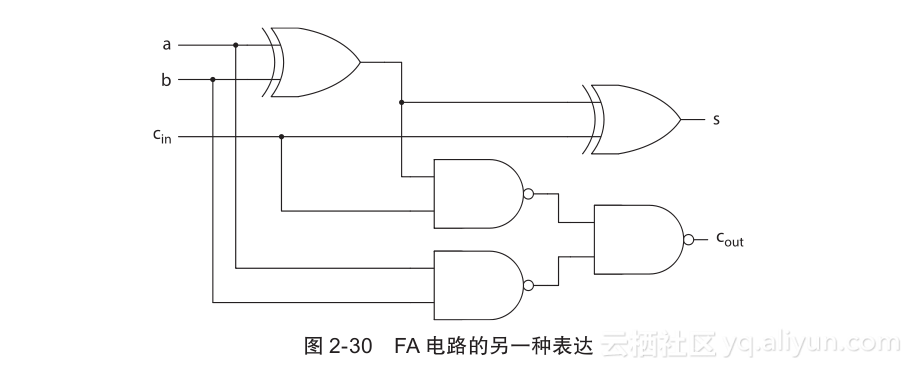

作为一种选择,s和cout表达式也可以用异或门写成如公式(2-9)所示,这样就简化了电路的门级结构,如图2-30所示。然而,这个解法将导致比公式(2-8)所实现电路的更长的传输延迟。

传输延迟估计

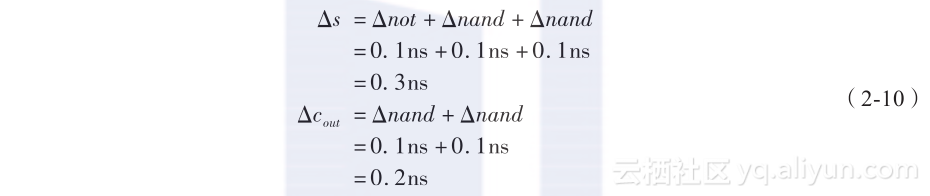

假设与非门有0.1ns的延迟,公式(2-10)估算了公式(2-8)中信号s和cout的传输延迟,用符号Δ表示。信号s和cout的SOP表达式分别有三级和二级的逻辑门。在信号s和cout的延迟估算中我们忽略掉了线路延迟。

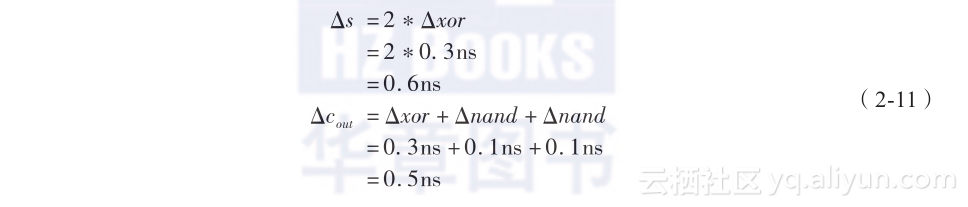

公式(2-11)展示了公式(2-9)中信号s和cout的延迟估算,SOP表达式中的异或门有0.3ns的延迟:

2.8.2 多路选择器

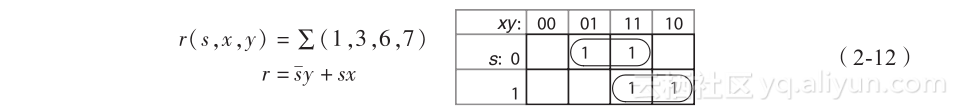

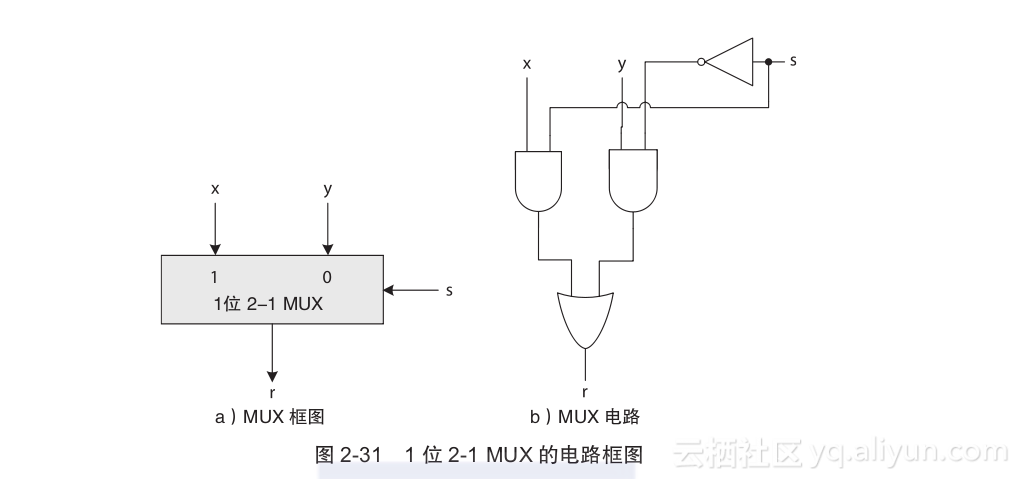

1位2-1的多路选择器,或者缩写MUX,是如图2-31所示的简单组合电路。输入x和y都为1位数据,信号s(选择器信号)导致MUX输出x或者y。如电路框图所示,标记1和0分别用来标记x和y,反映在MUX的真值表里(表2-9)。当s = 0时,MUX输出y,当s = 1时,MUX输出x。其最小SOP表达式由以下式子决定:

例如,当s = 0时,公式(2-12)计算结果符合预期,即r = y,如下所示:

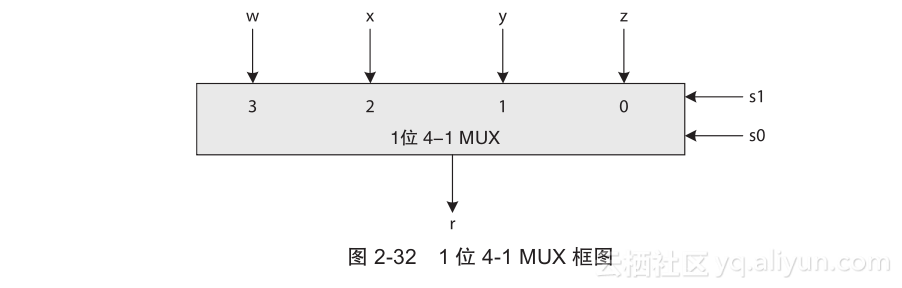

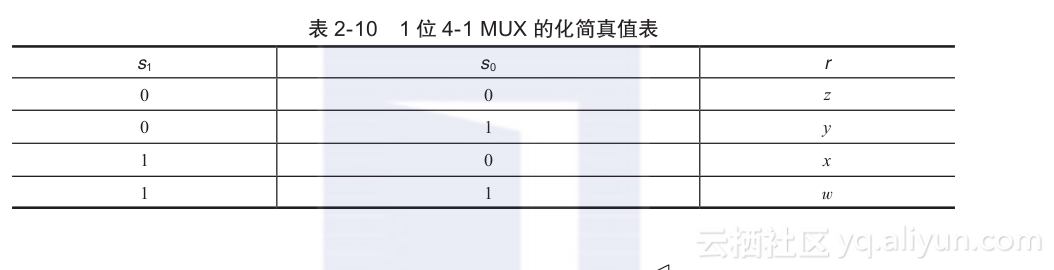

类似地,当s = 1时,MUX输出(或者选择)输入x。图2-32展示了拥有4位输入w、x、y和z的1位4-1的MUX电路框图,输入分别标记为3到0的数字。MUX需要两个选择信号,标记为s1和s0。表2-10展示了其简单的真值表。其扩展真值表有6个输入,比我们使用K图所允许的4个输入要大。除了使用K图,有两种方法来确定4-1 MUX的SOP表达式: 1)用Espresso软件;2)对有4个输入和2个选择信号的公式(2-12)进行推算。这就是当s1s0 = 0 = (00)2时,MUX将输出z,当s1s0 = 1 = (01)2时,输出为y;当s1s0 = 2 = (10)2时,输出为x,当s1s0 = 3 = (11)2时,输出为w。其最小SOP表达式为:

例如,当s1s0 = 2 = (10)2时,公式(2-13)计算结果符合预期,为r = x,如下所示:

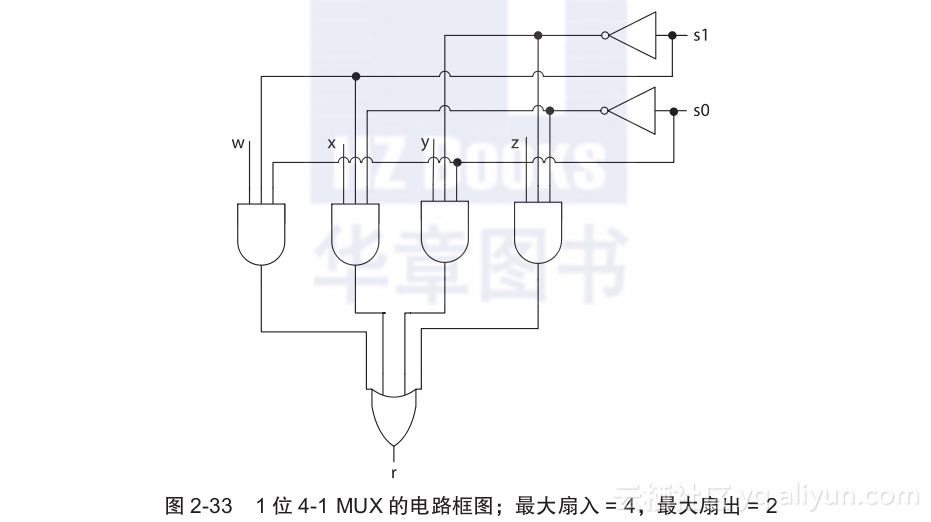

4-1 MUX的电路框图如图2-33所示。当MUX的大小增大,其扇入和扇出需求也相应地增大。考虑上述的2-1和4-1 MUX。它们最大扇入和扇出需求分别为2和2以及4和3。大型MUX,如果使用现在讨论的方法去设计,那么将导致扇入和扇出问题。在第3章中,我们将讨论大型组合电路的设计方法,首先将大型设计问题分为多个小型问题,然后对于每一个小型问题,使用这一章学到的方法去解决。之后小型电路将组合在一起形成大型组合电路,其可以避免任何的扇入和扇出问题。

2.8.3 译码器

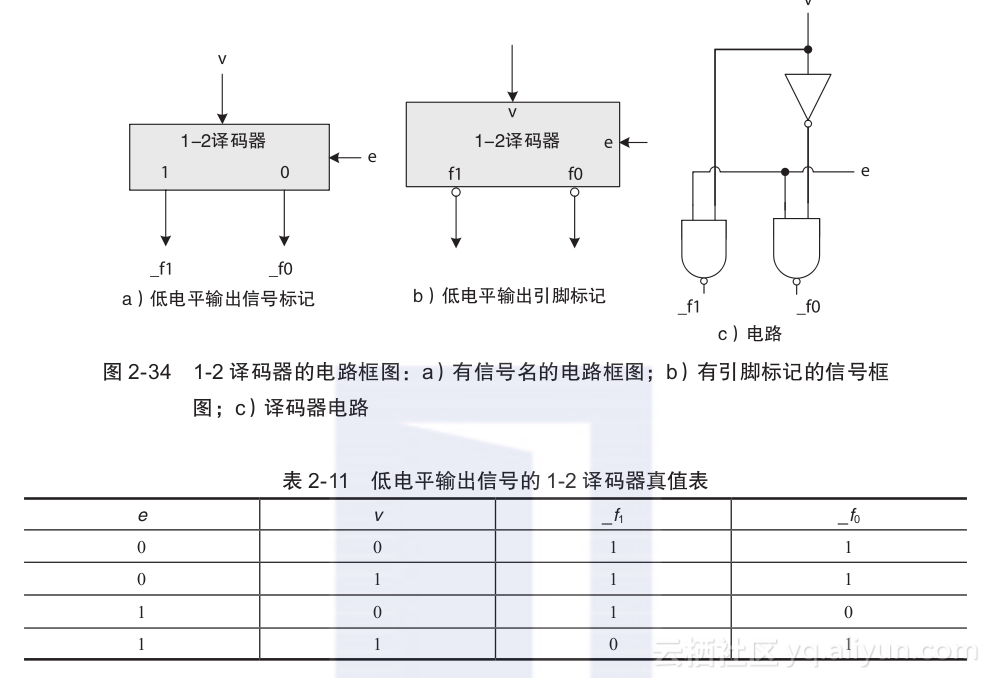

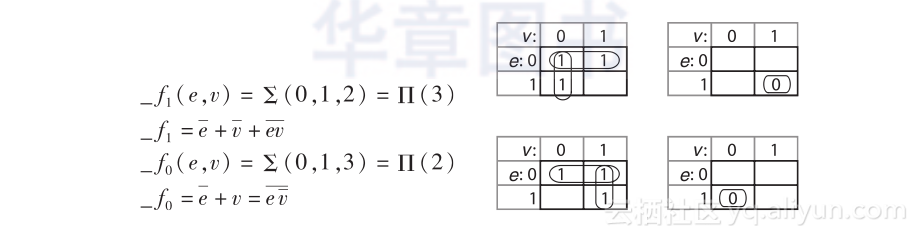

低电平输出的1-2译码器电路框图如图2-34所示。低电平标记引脚通常在基础引脚上加一个气泡表示,如图2-34b所示。然而,图2-34b中的气泡不仅仅是简单的非门表示。表2-11展示了译码器的真值表。只有一个或者没有_?f1和_?f0输出有效,这依赖于信号v和e的值。当e = 1且v = 0时,_?f0 = 0(有效)。当e = 1且v = 1时,_?f1 = 0(有效)。否则,当e = 0(不活跃)时,_?f1和_?f0都为1(无效)。

信号_?f1和_?f0的表达式可以表达为SOP或者POS。然而在这个例子中,对于这些信号的SOP或者POS表达式都是一样的。只有与非门译码器电路只有一个逻辑门的延迟,不包括非门(图2-34c)。

大型译码器也可以运用不同的方法来设计避免扇入和扇出的问题。译码器有许多应用,可以用于设计例如一些内存或者CPU数据通路。译码器可以用于解释内存地址,这样地址的内容可以进行读写操作。当需要写入一个寄存器文件时(第1章),译码器也可以用于译码一个寄存器数值。

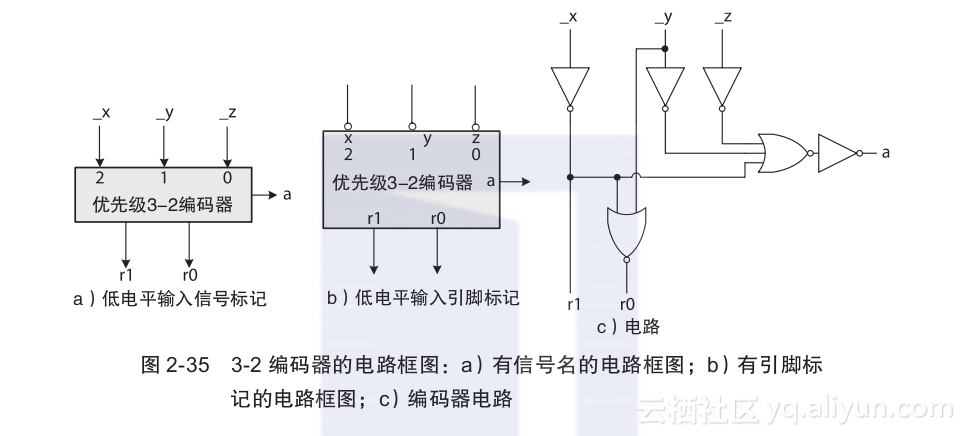

2.8.4 编码器

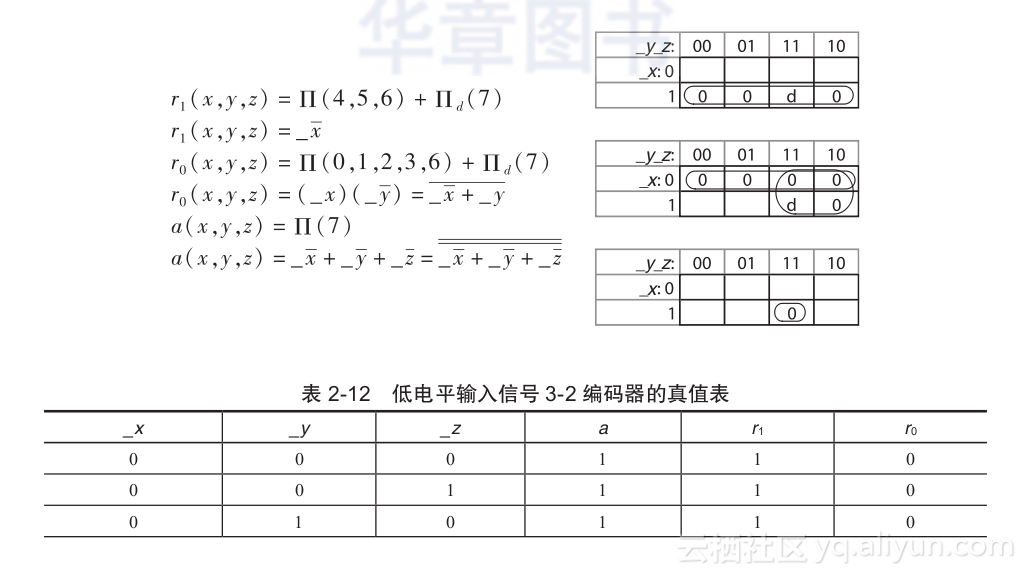

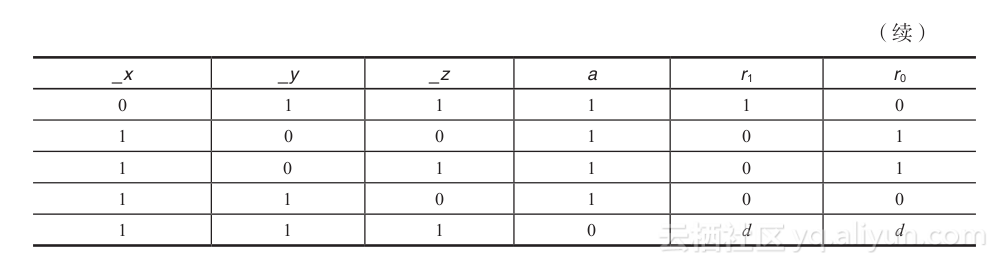

低电平输入信号的3-2编码器的电路框图如图2-35a所示,且低电平标记引脚也被标记为一个小圆圈,如图2-35b所示。表2-12展示了编码器的真值表。在表中输入信号用0~2的数字来表示。编码器电路输出一个由活跃的输入定义的数字。例如,当_z = 0(活跃的),_y = 1(不活跃)且_x = 1(不活跃),编码器输出r1r0 = (00)2 = 0,正确识别有效信号_z为数字0。然而,当编码器的输入没有一个是活跃的时候,定义另外一个输出信号a(输入活跃)是有必要的。当a = 1(有效)时,表示一个或者多个信号_x、_y和_z为活跃的,这样2位输出r1r0被定义为活跃的信号。另一方面,当a = 0(无效)时,输出r1r0 = (00)2被忽略。

两个或两个以上的编码器输入在同一时间变为活跃是有可能的。例如,当_x = 0,_y = 0

和_z = 1时,编码器必须遵照某一信号优先级输出信号_x或者信号_y对应的数字。这样的编码器叫作优先级编码器。

表2-12展示了3-2优先级编码器的真值表(图2-35),输入信号_x有最高优先级而

_z的优先级最低。当_x = 0(活跃)、_y = 0(活跃)和_z = 1(非活跃)时,编码器输出a = 1和r1r0 = (10)2,标记_x为最高优先级的输入信号。

信号a,r1和r0的POS表达式如下所示:

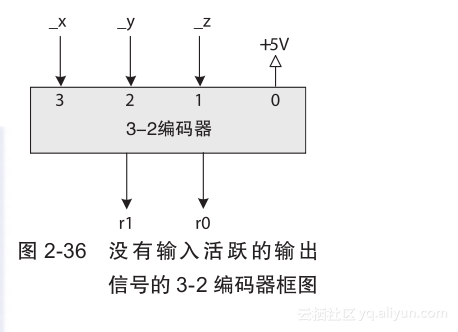

编码器也可以设计为没有输出信号a,如图2-36所示。它被设计成4-2的编码器形式,没有信号a,但是输入数字0是未使用的,且与电源连接(或者高电平有效的输入接地),这样可以有效地改变为3-2编码器。当输入信号_x、_y和_z中没有一个为活跃的时候,编码器的输出为r1r0 = (00)2(原书有误——译者注),表示输入是不活跃的。当一个或多个输入信号变为活跃时,编码器分别输出3、2和1来定义_x、_y和_z为活跃信号。这样消除了产生信号a相应的逻辑,并在设计时减少了电路信号,如图2-35所示。连接到电源的输入可以在内部实现。再次地,在设计一个大型编码器时,将用不同的方法来避免扇入扇出的问题。

编码器也可以拥有许多应用,特别是在设计母版中。例如,当外部信号变为有效时,编码器可以快速地通知CPU。有效外部信号可以由一个输入/输出设备产生或者由板上的给CPU提供服务的模块产生。