2.7 其他逻辑门

作为对之前标准逻辑门的补充,这节里将介绍一些其他对设计数字系统来说必需的其他逻辑门。这些逻辑门有缓存、集电极开路(OC)缓冲区和三态缓存。

2.7.1 缓存

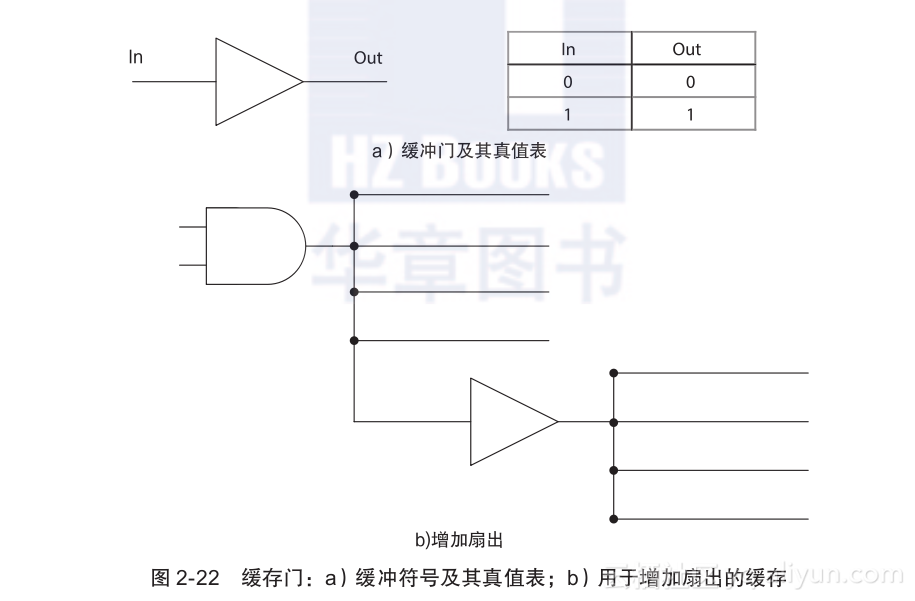

缓存的符号和真值表如图2-22a所示。一个缓存不会改变其输入信号;只是简单地放大它。假设与门的扇出为5,缓存可以增加与门的扇出至5~9,如图2-22b所示。

2.7.2 集电极开路缓冲区

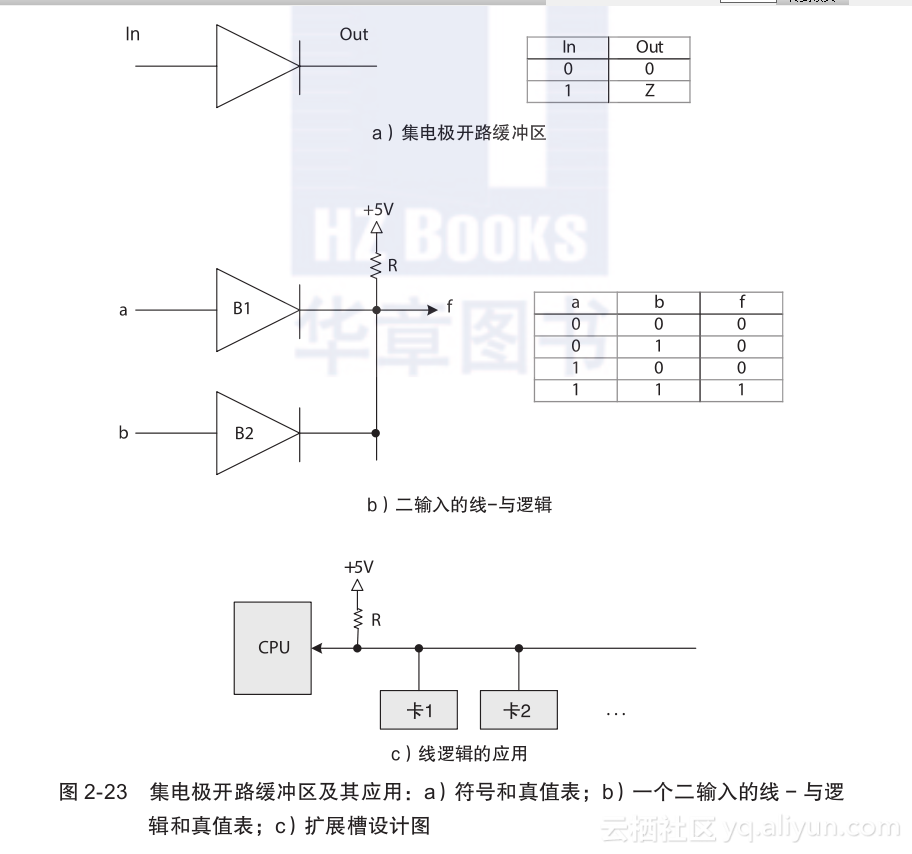

OC缓冲区和缓存门类似,除了当其输入为逻辑1时,其输出变为高阻抗,如Z(图2-23a)所示。高阻抗信号既不是逻辑0也不是逻辑1,而是显示为电隔离,就像导线是“浮动”的而不是连接的。图2-23b展示了有两个OC缓冲区的电路。每一个逻辑门的输出不是0就是Z,这样输出可以连接到一起产生一个输出信号f。Z输出可以使用连接到其他电源(例如5.0V)或者电源接地(0.0V)的电阻“拉起”或者“拉下”变为逻辑1或者逻辑0。图2-23b中的Z输出是拉起。

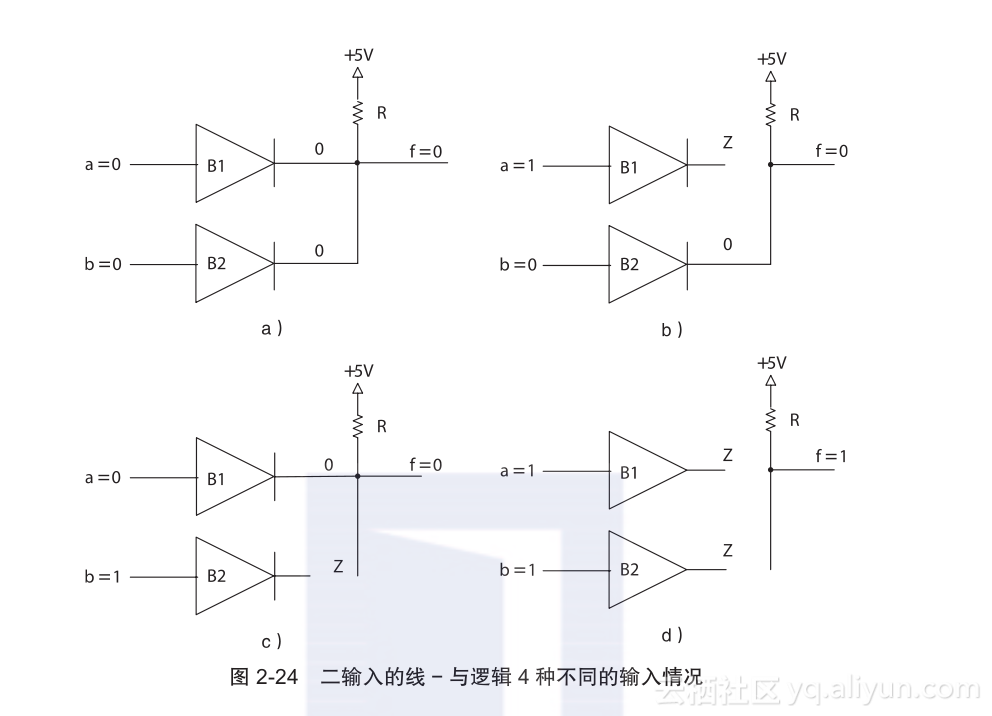

图2-24展示了使用图2-23b中有两个输入a和b的电路的高阻抗输出行为。当a = 0和b = 0时,OC缓冲区B1和B2输出0,这样就将f连接到地,即逻辑0(图2-24a)。当a = 1和b = 1时,OC缓冲区B1和B2输出为Z(浮动的);这就让f连接到电源,即为逻辑1

(图2-24d)。当a = 0和b = 1或者a = 1和b = 0时,其中一个缓存输出0而其他缓存输出Z,这样就把f和逻辑0相连,如图2-24b和图2-24c所示。4个例子总结了一张如图2-23b的真值表。真值表展示了一个与逻辑,和这个例子中的叫作线-与逻辑的电路。线逻辑电路可以拥有很大的扇入。

线-与和线-或逻辑是两种常见的线逻辑电路。例如,线逻辑电路可以用于设计有扩展槽的计算机系统。在这个例子中,线逻辑电路可以在计算机系统中通过在一个叫作设备控制器接口(DCI)的计算机扩展槽中插入扩展卡来增加功能,例如一个有n个输入的线-或逻辑电路,可以对n个信号进行与操作,信号可以来自不同的设备,如图2-23c所示。这个设备接口将在第9章中更详细地进行讨论。

2.7.3 三态缓存

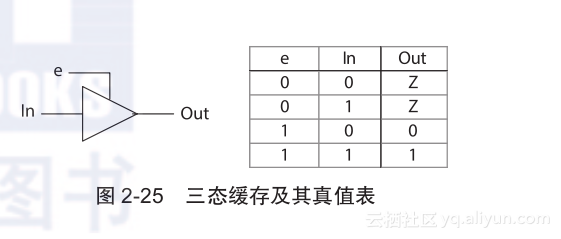

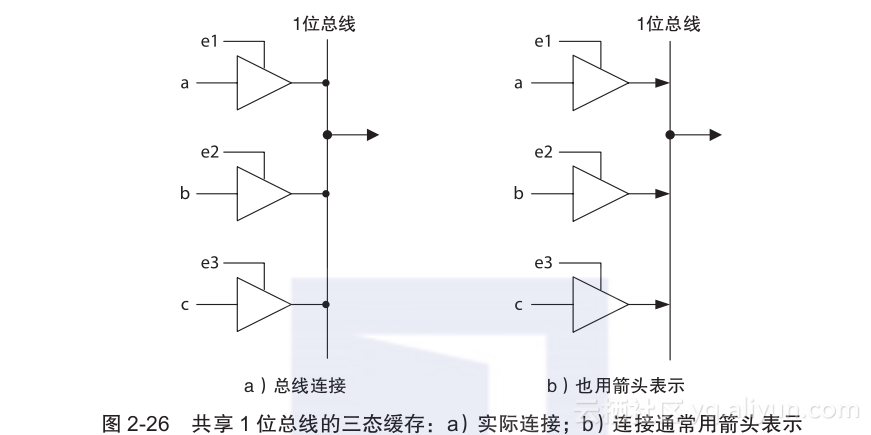

图2-25展示了三态缓存及其真值表。三态缓存是一个缓存和一个OC缓存的组合。当使能时(e = 1),它像一个缓存一样工作,但当禁止时(e = 0),其输出变为Z。三态缓存用于当输入为两个或多个信号需要共享一条叫作总线的线路的情况中。通常,总线可以用于很多条线路。图2-26展示了三态缓存到1位总线的连接。每一次一个使能信号e1、e2或者e3可以使得对应的信号a、b或c放到总线上。其他禁用的三态缓存将输出Z(“浮动的”),这样可以使其与总线隔离。

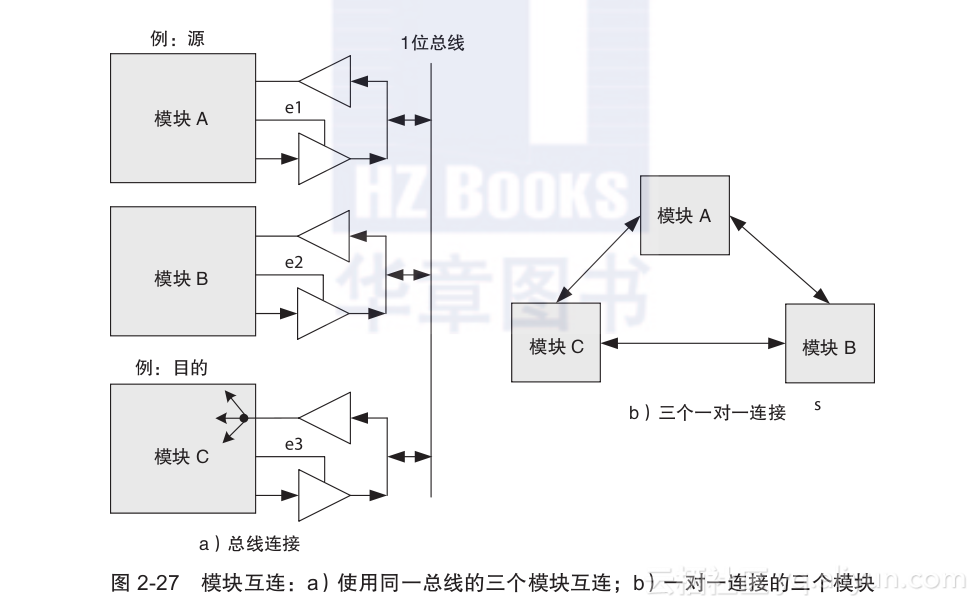

如果一个电路模型输出到总线和从总线中输入,总线连接可以是双向的。图2-27a展示了一个双向总线连接的例子,使用一个缓存从总线中输入和一个三态缓存输出到总线中。在双向总线中传输的数据项有一个源模块和一个目的模块。源模块用一个三态缓存在总线中放置一个数据项,目的模块用一个缓存输入数据。如果总线扇出在目的模块中大于1,缓存可以保护系统在源模块中免受扇出干扰;这就是,一个总线信号在目的模块中与两个或者多个逻辑门相连,如图2-27a中的目的模块C。

总线降低了互连的开销。其可以代替多个在多个模块中一对一的连接(图2-27b),只要数据(位数)通过总线发送的速度(频率)可以足够大来处理负载。这个总线数据速度被称为带宽。例如,在图2-27a中,每10ns一位数据可以在一位总线上传输,如果使能信号e1、e2和e3每10ns只有一个有效,或者其中一个使能信号在多个10ns中有效。可以在每10ns中传送1位数据的1位总线的带宽与可以在每100ns中可以传送10位数据的10位总线的带宽是一样的;在100ns中,两条总线都可以传送10位数据。这样,总线的宽度(线路的数目)和总线的速度(频率)决定了总线的带宽。

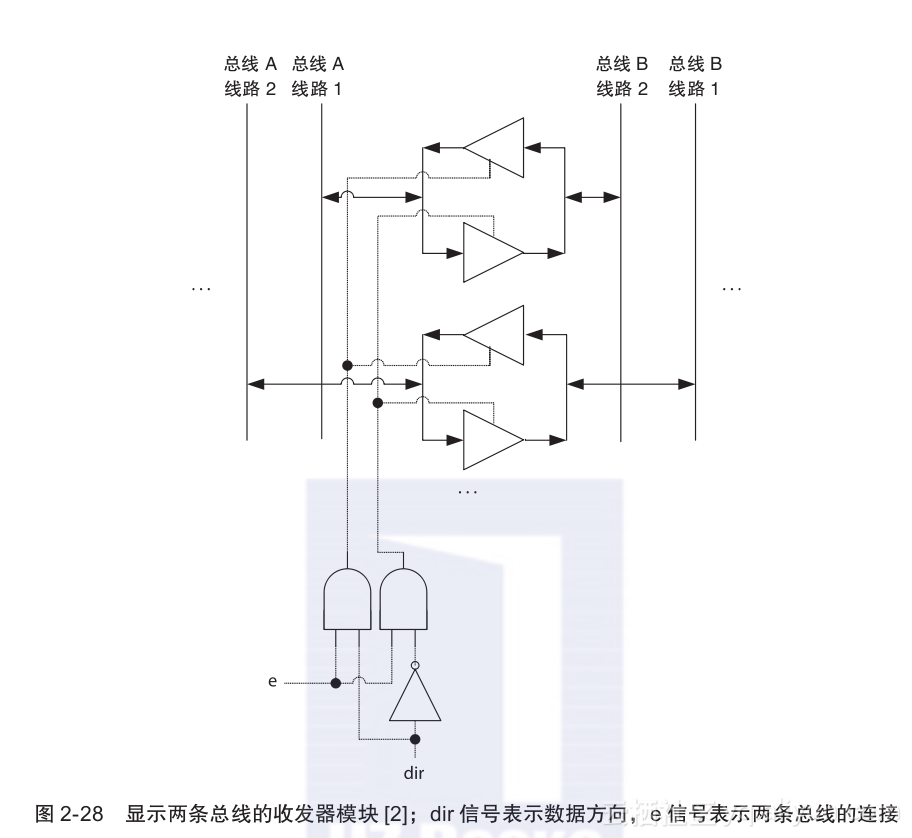

两个三态缓存可以用于收发器(传输/接收)电路连接,例如,如图2-28所示的两条分开的总线。每一个收发器电路都有两条总线之间的双向连接。方向(dir)信号决定了数据的方向,从总线A到总线B或者从总线B到总线A。当使能(e)信号有效时,数据连接到两条总线上,并保持它们一直连接。