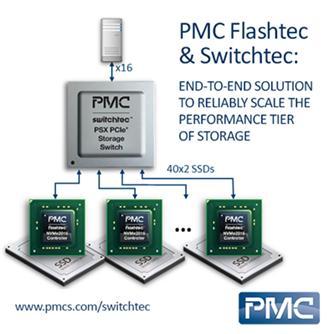

2015年8月10日,引领大数据连接、传送以及存储,提供创新半导体及软件解决方案的PMC公司宣布,推出业界首款PCI Express(PCIe)存储交换芯片以及全球速度最快的SSD控制器。采用PMC的第二代Flashtec NVMe 控制器的SSD能实现高达百万的IOPS及其20TB的闪存容量。而连接这些高性能、低延迟SSD的系统需要一系列强大的PCIe交换方案。PMC的Switchtec™ PSX PCIe 存储交换芯片具备可编程及先进的诊断功能,并具备大规模部署所需的多端口。SwitchtecPCIe存储交换芯片及FlashtecPCIe控制器提供了端到端的解决方案,为下一代闪存系統的部署铺平道路。

超大规模数据中心及企业级数据中心选择PCIe的原因在于PCIe提供了SSD与主机处理器之间的最高的速度及最低的延迟,故而比SAS及SATA具有显著的性能优势。Demarteck独立测试显示,采用Flashtec控制器的单个SSD在一个微软SQL数据库上运行OTLP负载时能提供高于运行8个SATA SSD时2.5倍的带宽,且相较于其他PCIe SSD,Flashtec能提高近一倍IOPS。

然而,虽然具备这些显著的性能优势,由于市面上缺乏存储级别的PCIe交换方案,PCIeSSD尚未得到广泛部署。现有的PCIe交换设备不具备高可用性及存储功能来连接或扩展SSD。PMC的Switchtec PSX芯片解决了存储扩展方面的挑战,能有效推动PCIe SSD部署。

业界首款企业级PCIe存储交换芯片

PMC的Switchtec PSX存储交换芯片的设计宗旨在于以业内最低的功耗对高性能存储系统中的PCIe闪存设备进行扩展。通过PSX构建的系统功耗能比同类系统低60%,每机架约节省1000瓦的电能。在一个典型的闪存阵列中,使用一个PSX就能抵上原本使用4个芯片的系统,由此降低设计复杂度,降低原材料的总成本,并改善平均故障间隔时间,从而显著提升系统的可靠性。

PSX具备以下功能:

业内最为灵活的端口分叉,每端口可连接x2到x16条通道;

最高的端口密度及不透明桥(NTB)密度,最高可连接48个端口及48个不透明桥;

最高的交换分组密度,最高可分为24组,以高效利用系统资源;

先进的故障隔离及突发性插拔,以避免系统崩溃;

业界首款带有集成的可编程处理器,系统客户可利用PSX软件开发包来提升PCIe交换的功能及故障处理能力;

业界首款带有集成的机箱管理方案,简化软件开发;

先进的诊断及排障功能,用以甄别、诊断及排除故障;

PMC的第五代SERDES,实现低功耗的、同行最优的信号集成;

支持SRIS提供线缆连接的PCIe,降低系统设计成本。

最高容量、最佳性能及最优可靠性的NVMe控制器

PMC的第二代NVMe控制器NVMe2032及NVMe2016是业界首款集成了DDR4 DRAM的SSD控制器,减少瓶颈并实现最大吞吐量。Flashtec具有灵活及其可编程的架构,让客户得以按照成本及负载需求等的要求对SSD进行定制化,以提供所需的耐久度、性能及容量等。先进的低密度奇偶校验(LDPC)) 纠错码(ECC)能支持最新NAND技术实现的节点,包括3-D及TLC NAND等等。这两款控制器均针对能耗效率进行了优化,包括处理器核的自动休眠及自主的功耗降低功能。

Micron存储市场营销副总裁Eric Endebrock表示“我们非常高兴能与PMC合作,通过他们高效能的 LDPC控制器来实现Micron的3D NAND技术。这些成果将帮助我们的客户处理关键应用以及优化虚拟机上的负载。”

SK Hynix NAND产品规划副总裁S.H Choi 表示“我们期待与PMC合作,向超大规模以及企业级数据中心市场提供使用SK Hynix 3D NAND以及PMC领先的PCIe SSD控制器的SSD。”

PMC的第二代Flashtec™ NVMe™ 控制器具体规格包括:

百万IOPS (4KB)

大于20TB的闪存容量(16TB闪存容量采用256Gb的闪存密度);

支持3-D、TLC、企业级MLC、MLC及带有Toggle或ONFI接口的SLC NAND闪存等;

PCIe 3.0x8 或两个独立的PCIe 3.0x4(主用/主用及主用/备用);

多达32个独立的闪存通道;

标准的企业级NVMe主机控制端口;

加密(XTS-AES-256);

闪存通道RAID.