|

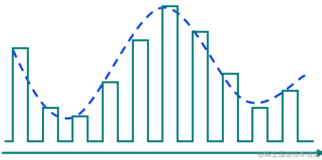

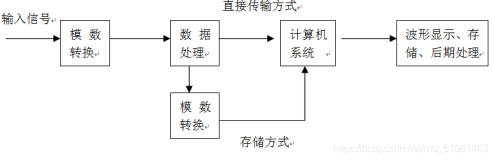

数字基带传输系统的基本组成框图如图 4-9 所示,它通常由脉冲形成器、发送滤波器、信道、接收滤波器、抽样判决器与码元再生器组成。系统工作过程及各部分作用如下。 |

|

图 4-9 数字基带传输系统方框图 |

| 脉冲形成器输入的是由电传机、计算机等终端设备发送来的二进制数据序列或是经模数转换后的二进制(也可是多进制)脉冲序列,它们一般是脉冲宽度为 |

| 基带传输系统的信道通常采用电缆、架空明线等。信道既传送信号,同时又因存在噪声 |

数字基带系统的工作原理

2015-12-26

2322

版权

版权声明:

本文内容由阿里云实名注册用户自发贡献,版权归原作者所有,阿里云开发者社区不拥有其著作权,亦不承担相应法律责任。具体规则请查看《

阿里云开发者社区用户服务协议》和

《阿里云开发者社区知识产权保护指引》。如果您发现本社区中有涉嫌抄袭的内容,填写

侵权投诉表单进行举报,一经查实,本社区将立刻删除涉嫌侵权内容。

简介:

目录

相关文章

|

7月前

|

算法

异构计算

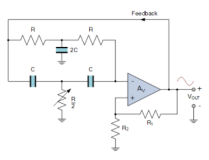

双T型振荡器主要特点和工作原理介绍

双T振荡器是另一种类型的RC振荡器,它产生正弦波输出,用于类似于电桥桥振荡器的固定频率应用。双T型振荡器在反相放大器的输出和输入之间的反馈回路(因此得名)中使用两个“Tee”形 RC 网络。

1473

0

0

|

网络协议

5G

计算机视觉

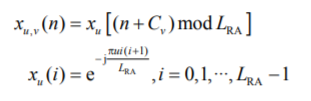

随机接入 |带你读《5G 无线系统设计与国际标准》之十一

随机接入过程用于获得上行同步,完成随机接入过程之后,终端就可以与基站进行上行通信。与 LTE 类似,NR 支持基于竞争的随机接入及基于非竞争的随机接入。

4017

0

0

|

6月前

|

芯片

|

9月前

|

算法

异构计算

Windows

m基于FPGA的DQPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

m基于FPGA的DQPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

261

1

1

|

10月前

|

数据采集

传感器

编解码

LabVIEW控制Arduino采集多路模拟量、数字量(进阶篇—1)

数据采集,是指从传感器和其他待测设备的模拟和数字被测单元中自动采集信息的过程。能够实现数据采集功能的系统叫作数据采集系统。

194

0

0

|

算法

异构计算

m基于FPGA的全数字OQPSK调制解调器,包括成形滤波器、NCO模型、costas载波恢复

m基于FPGA的全数字OQPSK调制解调器,包括成形滤波器、NCO模型、costas载波恢复

125

1

1