1.2 逻辑设计

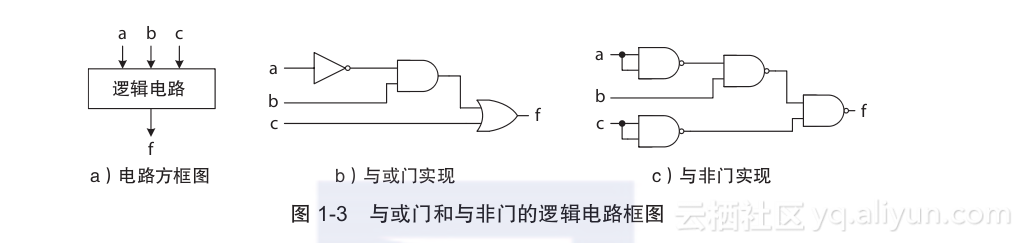

数字电路即逻辑电路,可以实现一个或多个布尔表达式,而每个布尔表达式均定义了一个或多个输入与单一输出之间的逻辑关系。输入和输出都由布尔变量命名,称为信号,每个信号的值或者为真(T)或者为假(F)。公式(1-2)定义了有a、b、c三个输入信号和一个输出信号f的逻辑电路布尔(逻辑)表达式。图1-3a显示了该电路的方框图。

表达式中的AND、OR和NOT为布尔逻辑运算符。晶体管构成的逻辑门用于实现每一种布尔运算符。现代集成电路使用数百万个逻辑门实现处理器这类复杂的逻辑电路。当两个输入都为1时,与(AND)门的输出为1(真);当至少一个输入为1时,或(OR)门的输出为1;非(NOT)门的输出值与输入值相反,如果输入为0(假)则输出为1,而输入为1(真)则输出为0。例如,当a = 0、b = 1且c = 0时,f的逻辑值由公式(1-3)决定:

除了非(NOT)之外的其他运算符可以被扩展至多于两个布尔变量,而其等价的逻辑门实现可支持两个或者更多个(不超过最大值)独立输入信号。还有其他的逻辑门,例如与非门(NAND)和或非门(NOR),这些逻辑门可以用更少的晶体管实现。与非门在逻辑上等价于与门后面跟着一个非门(与非逻辑),而或非门则等价于或非逻辑。一般而言,逻辑电路或者用与非门实现,或者用或非门实现。1.2.2节将讨论非门、与非门和或非门的晶体管组成。图1-3b显示了用非门、与门和或门(称为与或电路)实现表达式f的原理图,图1-3c为与其等价的与非门电路。

如表1-4所示,图1-3中的a、b和c的输入值有8种可能的组合。a、b和c可以组合起来构成一个3位二进制数(abc)2,其中使f = 1的5个取值abc = (001)2、(010)2、(011)2、(101)2和(111)2分别对应素数1、2、3、5和7。剩余的令f = 0的三个二进制数abc = (000)2、(100)2和(110)2则不属于素数。因此,公式(1-2)定义的逻辑电路每当三位输入值abc代表素数时输出1,否则输出0。表1-4a和表1-4b是逻辑表达式f的两种不同形式的真值表。随后将讨论等价表达式g。

1.2.1 电路最小化

尽管一个逻辑关系可以用若干个等价的布尔表达式表示,但我们的目标还是要找到一个具有以下特征的最小表达式:1)需要更少的硬件实现(即更少的门逻辑,更少的门输入,更少更短的连接线);2)实现该表达式的最终电路需要更短的时间产生输出结果。用布尔代数可以实现复杂表达式的最小化。

公式(1-4)描述了与公式(1-2)中f等价的g的逻辑表达式。用于实现表达式g的硬件部件要比实现表达式f的多。但是,如表1-4所示,与输出g和f相对应的每一项都是一样的。这证明公式(1-2)和公式(1-4)是等价的,两者描述了同样的函数关系,但公式(1-2)是最小化的。实现公式(1-2)的电路要比实现公式(1-4)的电路需要少得多的硬件,而且操作速度更快。

1.2.2 实现

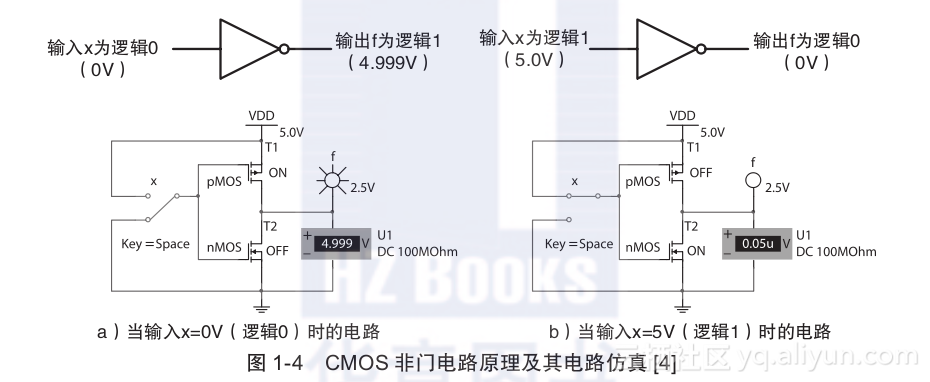

图1-4展示了使用一个p类和一个n类金属-氧化物半导体场效应晶体管(MOSFET)构成的非门电路原理图。该原理图称为CMOS(“C”表示互补,complement)电路,因为pMOS和nMOS晶体管是互补的;当一个晶体管处于关断(未导通)状态时,另一个处于开通(导通)状态。如图1-4a所示,当输入x的值为逻辑0(0V)时,pMOS晶体管变为开通状态而nMOS晶体管变为关断状态。这将使输出信号f的取值如期变为逻辑1,正如原理图中所示的指示灯点亮且电压表读数显示为4.999V。

在图1-4b中,当输入x为逻辑1(5.0V)时,结果相反。pMOS晶体管关断,而nMOS晶体管开通,输出f变为逻辑0,正如原理图中所示的指示灯熄灭且电压表读数显示为0V(0.05μV≈0V)。

老旧的大型计算机是使用低能效的门电路制造而成的,与之相比,现代芯片是采用高能效的CMOS门设计的。如图1-4所示,由于其中一个晶体管始终处于关断状态,CMOS非门基本上只在一个晶体管开通而另一个晶体管关断的情况下才消耗电能。当每次输入x从逻辑1变为逻辑0或者从逻辑0变为逻辑1电压时,这种情况才会发生。当然,如果x值的变换非常频繁,晶体管在开通和关断状态之间转换得也会非常快,这会使非门消耗更多的电能。

随着芯片上集成的晶体管的数量及其在开通和关断之间切换的速率同时提升,芯片运转所需的电能也随之增加,这相应地要求释放更多的热量以便冷却芯片。比如,Intel 80386处理器功率约为2W,而3.3GHz的Intel酷睿i7处理器则消耗大约130W的功率(65倍以上)。与过去的大型计算机和超级计算机相反,现代计算机系统采用风扇制冷系统。设计师必须考虑芯片要持续消耗多少电能,以免超出其温度承受范围而造成芯片工作失效甚至永久性损坏。功耗问题将在第6章中进一步讨论。

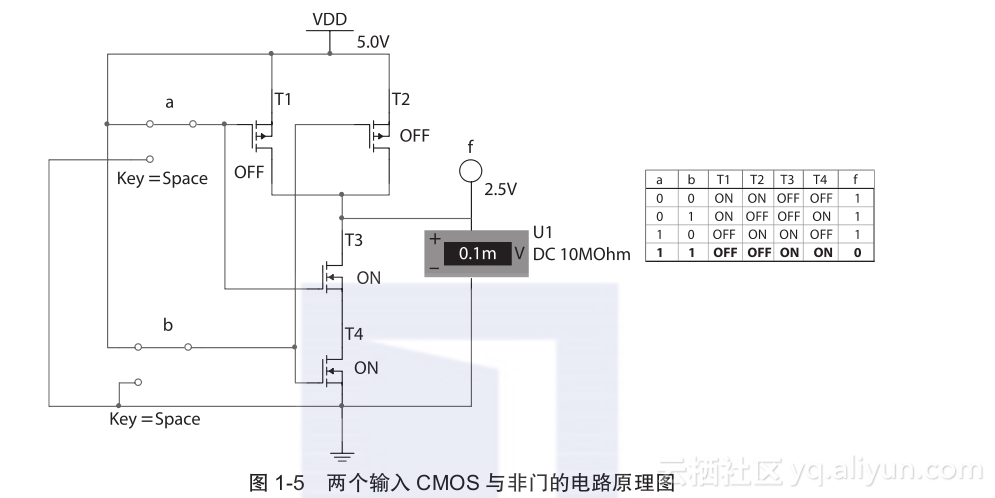

图1-5显示了两输入CMOS与非门的电路原理图。如图所示,两个并联的pMOS晶体管和两个串联的nMOS晶体管被连接到电源和地。当两个输入a和b都为逻辑1时,与非门输出逻辑0,此时两个nMOS晶体管均为开通状态,而两个pMOS晶体管均为关断状态。图中的真值表还显示了输入a和b的4种可能取值及其输出f的对应取值,以及晶体管的工作状态。

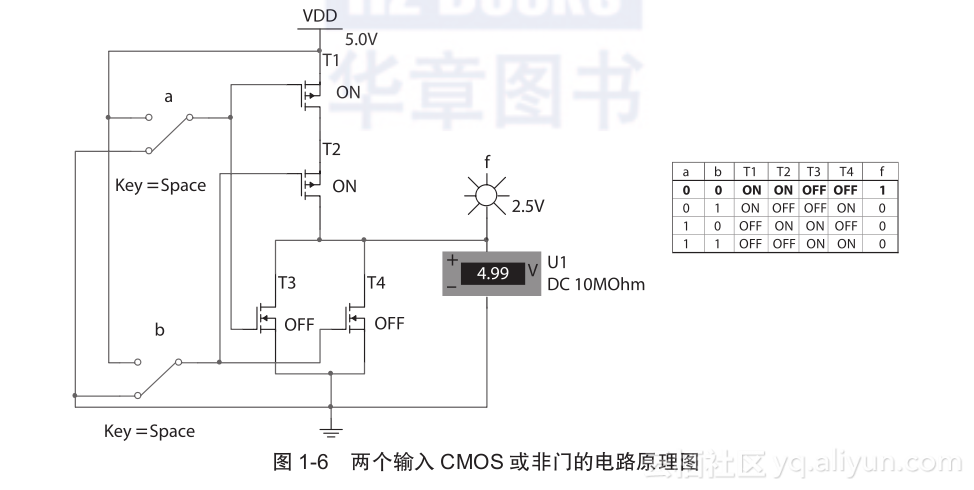

类似的,图1-6展示了两输入或非门电路原理图。在此图中,两个pMOS晶体管串联而两个nMOS晶体管并联。当至少有一个nMOS晶体管为开通状态时(a = 1、b = 1或者a = 1且b = 1),输出为逻辑0(即0)。当两个pMOS晶体管都为开通状态且两个nMOS都为关断状态时(a = 0且b = 0),输出为逻辑1(即1)。

1.2.3 电路类型

布尔表达式既可描述组合电路,也可描述时序电路。组合电路的输出仅仅取决于电路当前的输入值。公式(1-2)和公式(1-4)都是简单组合电路的表达式。而图1-1中的加法器、乘法器和数据选择器模块则是更复杂的组合电路,每个电路都产生多位输出,并基于其相应的当前输入逻辑值并行生成输出结果。

相反,时序电路则根据此前输入的逻辑值存储特定的状态信息。例如,输出0、1、2、3等值的计数器就是时序电路。它根据当前的输出值(例如2)生成序列中的下一个取值(例如3)。当前的计数值会作为计数器的状态存储在计数器内部。有时,时序电路也会根据一个或多个输入来决定下一个状态。例如,递增/递减计数器需要一个控制信号来决定计数方向。如果计数器的当前输出为2,则递减计数时下一输出为1,递增计数时下一输出为3。

图1-1中所示的寄存器和控制器也属于时序电路。当控制器发出信号时,每个寄存器都在内部存储固定取值并一直保持该值,直到控制器再次发出信号。控制器根据一系列的状态生成控制信号去控制数据通路。一个或者多个控制信号可以用于控制数据通路中每一个模块的功能。图中,一个控制信号用于控制寄存器和数据选择器。如果逻辑值1用于寄存器加载而0用于保持,则当其控制信号为1时,寄存器就会从其输入端加载逻辑值,而当控制信号为0时,则保持其当前值不变。

假设图1-1中的控制器是三状态控制器,实现下述三个简单功能,并每次求出两个输入的和:

状态1:从存储器加载数据至寄存器1。

状态2:从存储器加载数据至寄存器2。

状态3:选取求和结果并将其存入寄存器3。

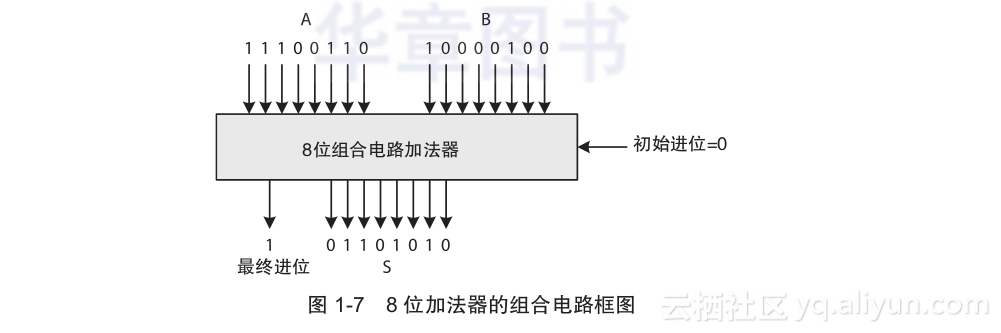

通常,一个实现诸如算术运算功能之类的电路既可以设计成组合电路,也可设计成时序电路。组合逻辑算术运算电路可以一步生成其输出结果,且并行生成所有的输出位,如

图1-7所示。相反,时序逻辑算术运算电路用若干步串行生成最终的输出。在每一步中,时序电路都根据前一步的结果生成当前一步的输出。这个过程重复固定的次数,直到产生最终的输出结果。

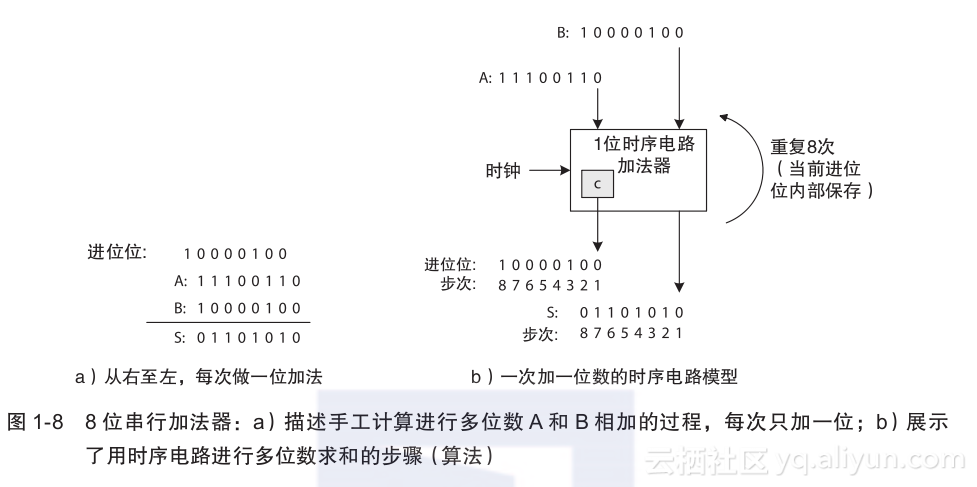

例如,一个8位的时序电路加法器可以重复8次利用单位加法器生成最终的8位和,如图1-8所示,这和我们手工进行两个数的加法运算非常相似,每次一个数字,从右往左运算。图中,在每一步运算过程中,从A数中取出一位,从B数中取出一位,再加上前一步生成的进位位生成下一步的和值。加法器内部保存进位位用于下一步操作。图中也展示了内部存储的进位位的各次运算结果。内部进位位初始值为0。时钟信号控制数A和数B下一位进入加法器的时间以及生成和S的下一位的时间。经过8次运算,最终的8位和S

就生成了。

乘法器也可以使用组合电路或者时序电路来设计。组合电路的乘法器在同一时间运用多个组合加法模块来生成乘积。相反,时序电路的乘法器可以重复地使用组合加法器或者时序加法器来生成乘积。相比之下,组合运算电路通常比与其等价的时序电路速度要快,但是也要消耗更多的硬件资源。

1.2.4 计算机辅助设计工具

布尔代数的规则也可通过软件实现,并且已经被集成到许多逻辑设计CAD工具中。设计师通常使用HDL,或者更具体地说,一种寄存器传送语言(RTL)来描述数字电路,例如Verilog和VHDL,后者即超高速集成电路(VHSIC)HDL。虽然可以在RTL中直接使用布尔表达式,但设计师通常会使用诸如“if-else”语句这样的高层次描述方式来描述电路。例如,下列语句描述了图1-1中数据选择模块的行为,其中x用于选择加法器(“和值”)或者乘法器(“乘积”)的输出作为最终结果:

以上的“if-else”语句与公式(1-5)中的逻辑表达式等价,其中s、p和r分别表示“和值”的一位、“乘积”的一位和“结果值”的一位:

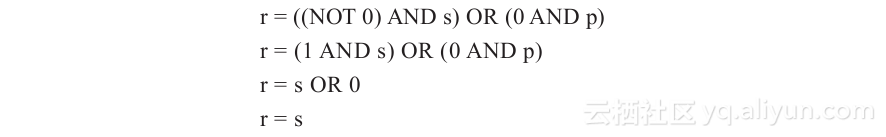

r = ((NOT x) AND s) OR (x AND p)(1-5)当x = 0时,“结果值”即为“和值”,在公式(1-5)中取r的一位、s的一位和p的一位。

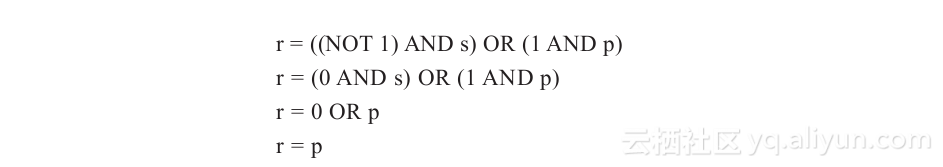

相反,当x = 1时,r将变为p,如下所示:

设图1-1中的sum、value1和value2都是8位数,则HDL语句“sum = value1 + value2”中的+运算符实现了类似图1-7中的8位加法器的功能,此处进位输入和进位输出被忽略。

RTL描述可以用于仿真,以验证电路描述的准确性。然后,RTL描述可以被综合(翻译)成被称为网表的等效最小电路表达,用于进一步的仿真,以验证电路的时序要求。最后,利用FPGA,网表可以被自动地映射到硬件上,生成逻辑电路。

组合和时序电路将分别在第2章、第3章和第4~6章详尽讨论。